4.1ISE套件

4.1.1ISE的特點(diǎn)

4.1.2ISE的功能

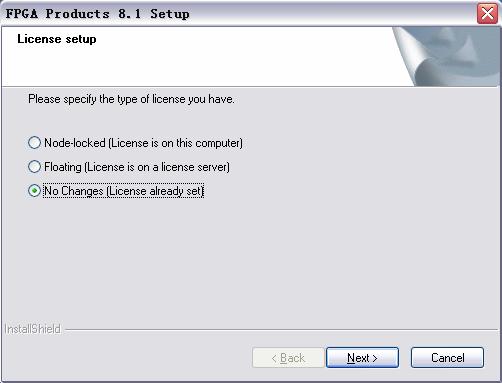

4.1.3ISE的安裝

4.1.4ISE的用戶(hù)界面

4.2基于ISE的設(shè)計(jì)輸入

4.2.1新建工程

4.2.2代碼輸入

4.2.3代碼模板的使用

4.2.4Xilinx IP Core的原理與應(yīng)用

4.3ISE基本操作

4.3.1基于Xilinx XST的綜合

4.3.2基于ISim的仿真

4.3.3基于ISE的實(shí)現(xiàn)

4.3.4基于目標(biāo)和策略的設(shè)計(jì)方法

4.3.5基于SmartGuide的設(shè)計(jì)方法

4.3.6比特文件的生成

4.3.7基于IMPACT的芯片配置

4.3.8功耗分析以及XPower的使用

4.4約束

4.4.1約束文件

4.4.2UCF文件的語(yǔ)法說(shuō)明

4.4.3引腳和區(qū)域約束語(yǔ)法

4.4.4時(shí)序約束語(yǔ)法

4.5調(diào)試?yán)鳌狢hipScope Pro

4.5.1ChipScope Pro工作原理

4.5.2ChipScope Pro操作流程

4.5.3ChipScope Pro開(kāi)發(fā)實(shí)例

4.6ISE與第三方EDA軟件

4.6.1ModelSim軟件的使用

4.6.2ModelSim和ISE的聯(lián)合開(kāi)發(fā)流程

4.6.3MATLAB軟件的使用

4.6.4ISE與MATLAB的聯(lián)合使用

4.6.5MATLAB、ModelSim和ISE聯(lián)合開(kāi)發(fā)實(shí)例

本章小結(jié)

第5章時(shí)序分析

5.1時(shí)序分析的作用和原理

5.1.1時(shí)序分析的作用

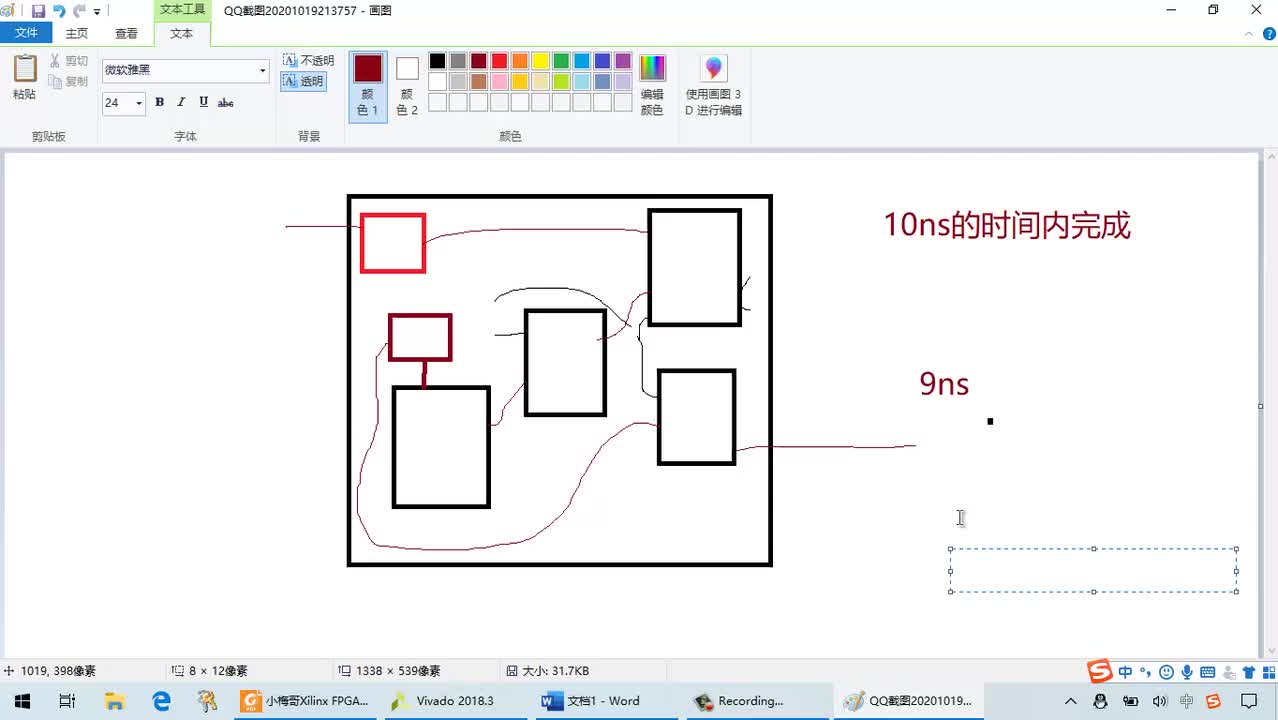

5.1.2靜態(tài)時(shí)序分析原理

5.1.3時(shí)序分析的基礎(chǔ)知識(shí)

5.2Xilinx FPGA中的時(shí)鐘資源

5.2.1全局時(shí)鐘資源

5.2.2第二全局時(shí)鐘資源

5.3ISE時(shí)序分析器

5.3.1時(shí)序分析器的特點(diǎn)

5.3.2時(shí)序分析器的文件類(lèi)型

5.3.3時(shí)序分析器的調(diào)用與用戶(hù)界面

5.3.4提高時(shí)序性能的手段

本章小結(jié)

第6章邏輯開(kāi)發(fā)專(zhuān)題

6.1Verilog HDL設(shè)計(jì)進(jìn)階

6.1.1面向硬件的程序設(shè)計(jì)思維

6.1.2“面積”和“速度”的轉(zhuǎn)換原則

6.1.3同步電路的設(shè)計(jì)原則

6.2Xilinx FPGA芯片底層單元的使用

6.2.1Xilinx全局時(shí)鐘網(wǎng)絡(luò)的使用

6.2.2CMT時(shí)鐘管理模塊的使用

6.2.3Xilinx內(nèi)嵌塊存儲(chǔ)器的使用

6.2.4硬核乘加器的使用

6.3代碼風(fēng)格

6.3.1代碼風(fēng)格的含義

6.3.2代碼書(shū)寫(xiě)風(fēng)格

6.3.3通用設(shè)計(jì)代碼風(fēng)格

6.3.4Xilinx專(zhuān)用設(shè)計(jì)代碼風(fēng)格

6.4.1串口接口與RS?232協(xié)議

6.4.2串口通信控制器的Verilog HDL實(shí)現(xiàn)

6.4.3RS?232設(shè)計(jì)板級(jí)調(diào)試

本章小結(jié)

第7章基于EDK的嵌入式系統(tǒng)設(shè)計(jì)

7.1可配置嵌入式系統(tǒng)(EDK)

7.1.1基于FPGA的可編程嵌入式開(kāi)發(fā)系統(tǒng)

7.1.2Xilinx公司的解決方案

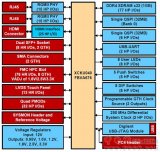

7.2Xilinx嵌入式開(kāi)發(fā)系統(tǒng)組成

7.2.1片內(nèi)微處理器軟核MicroBlaze

7.2.2PLB總線(xiàn)系統(tǒng)結(jié)構(gòu)

7.2.3IP核以及設(shè)備驅(qū)動(dòng)

7.3EDK軟件

7.3.1EDK設(shè)計(jì)的實(shí)現(xiàn)流程

7.3.2EDK的文件管理架構(gòu)

7.4XPS軟件典型操作

7.4.1XPS的啟動(dòng)

7.4.2利用BSB創(chuàng)建新工程

7.4.3XPS的用戶(hù)界面

7.4.4XPS的目錄結(jié)構(gòu)與硬件平臺(tái)

7.4.5在XPS加入IP Core

7.4.6XPS工程的綜合與實(shí)現(xiàn)

7.5SDK軟件典型操作

7.5.1SDK的用戶(hù)界面

7.5.2SDK的典型操作

7.5.3IP外設(shè)的API函數(shù)查閱和使用方法

7.5.4GPIO外設(shè)開(kāi)發(fā)實(shí)例

7.5.5其他外設(shè)開(kāi)發(fā)實(shí)例

本章小結(jié)

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論