Verilog的兩個誤區(qū):

使用Reg類 型還是Net類型:

Reg類 型只在過程塊中被賦值;而Net類型則在過 程塊外面被賦值或者驅(qū)動.

阻塞賦值和非阻塞賦值:

Verilog中競爭發(fā)生的條件:兩個或多個語句在執(zhí)行順序不同時導(dǎo)致不同的結(jié)果,則存在競爭.

Nonblocking不 是一個類型;

Blocking賦 值是一個單步過程,計算RHS,并更形LHS是不可中斷的.

七 條準(zhǔn)則:

1.時序邏輯和鎖存器,使 用非阻塞賦值

2.always塊中的組合邏輯,使用阻塞賦值

3.同一always塊,時序組合混合邏輯使用非阻塞賦值

4.通常情況下,在同一always塊中不要混合使用阻塞與非阻塞賦值

5.不 要在多個always塊中對同一變量進(jìn)行賦值

6.使用$strobe顯示非阻塞賦值得信號

7.不要用#0的過程賦值

Verilog中的分層事件隊列:

活動事件:阻塞賦值;計算非阻塞賦值的RHS;連續(xù)賦值;$display命令;計算輸入并改變原語的輸出.這些事件可能按照任意次序 調(diào)度.

非活動事件:#0的阻 塞賦值

非阻塞事件:更新非阻 塞賦值的LHS

監(jiān)視事件:$monitor命 令;$strobe命令

經(jīng)驗:

在always塊中使用非阻塞賦值來 產(chǎn)生時序邏輯和鎖存器

在always塊 中使用阻塞賦值來產(chǎn)生組合邏輯

在always塊 中使用非阻塞賦值來產(chǎn)生同一塊中的時序和組合邏輯

在純組合邏輯中使用非阻塞賦值可能 會導(dǎo)致功能錯誤

阻塞賦值和非阻塞賦值混 合使用的方式:

將組合邏輯賦值通過時序表達(dá)式表示

或者將組合邏輯賦值與時序邏輯分開,在獨(dú) 立的語句塊中描述

不推薦在同 一always塊中混合使用阻塞和非阻塞賦值

幾個關(guān)于非阻塞賦值的錯 誤理解:

錯誤1:無法使用$display命令顯示非阻塞賦值變量

正 解:非阻塞賦值變量的更新在所有$display命 令之后

錯誤2:#0讓一個賦 值在每個時間步的最后執(zhí)行

正解:#0只 會讓賦值語句進(jìn)入非活動事件隊列

錯誤3:在 同一always塊中對同一變量進(jìn)行多次非阻塞賦值是不允許的

正解:在IEEE 1364 verilog標(biāo)準(zhǔn)中定義了上述賦值,最 后一個非阻塞賦值起作用

模擬開始時候的困難:

不同的模擬器,不同的模擬選項導(dǎo)致開始模擬時現(xiàn)象不同

建議: 在0時刻通過非阻塞賦值設(shè)置reset信號;

第一個半周期設(shè)置clock為0

編寫Verilog代 碼的一些經(jīng)驗:

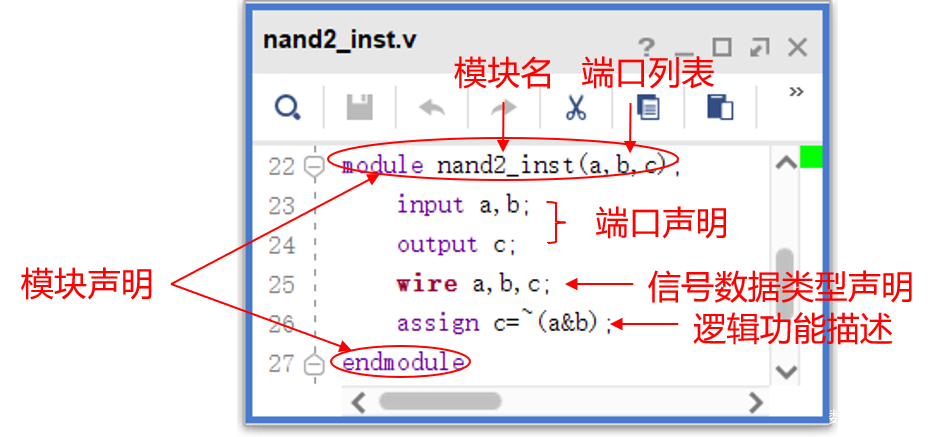

Verilog文件名和模塊名相同

不要在可綜合代碼中使用casex語句

當(dāng)在可綜合代碼中使用casez語句時 要小心

當(dāng)寫case語句時,對存在不關(guān)心的cases時使用casez,使用?代替Z來表示不關(guān)心的cases

Verilog編 寫狀態(tài)機(jī)相關(guān):

狀態(tài)機(jī)分類:Moore(輸 出只與當(dāng)前狀態(tài)相關(guān))和Mealy(輸出與 當(dāng)前狀態(tài)和輸入相關(guān))

二進(jìn)制編碼和One-Hot編 碼

狀態(tài)機(jī)的基本塊:下一狀態(tài) 度組合邏輯;時鐘同步的當(dāng)前狀態(tài)邏輯;輸出 組合邏輯

兩個always塊 寫狀態(tài)機(jī),使用三個always塊,如果輸出需要寄存

使用高效的One-Hot狀態(tài)編碼,組合輸出

經(jīng)驗:

每個狀態(tài)機(jī)作為一 個獨(dú)立的Verilog模塊

對 狀態(tài)進(jìn)行預(yù)定義,狀態(tài)賦值使用狀態(tài)名作參數(shù),不 要使用`define,多使用parameter

兩個always語句塊的狀態(tài)機(jī),一 個always用來描述狀態(tài)向量寄存器的時序邏輯.一 個用來描述下一狀態(tài)度組合邏輯.組合輸出可以通過連續(xù)賦值語句或者在下一狀態(tài)度組合always塊中描述.

電子發(fā)燒友App

電子發(fā)燒友App

評論