在文本窗口中輸入以下VHDL源程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

--*********************************************

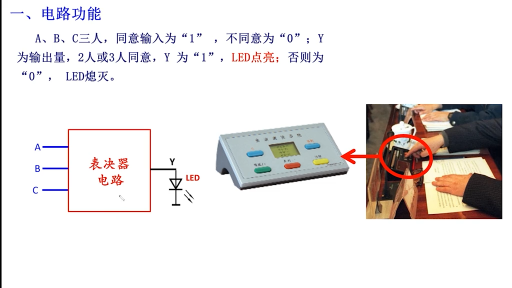

ENTITY majority_voter IS

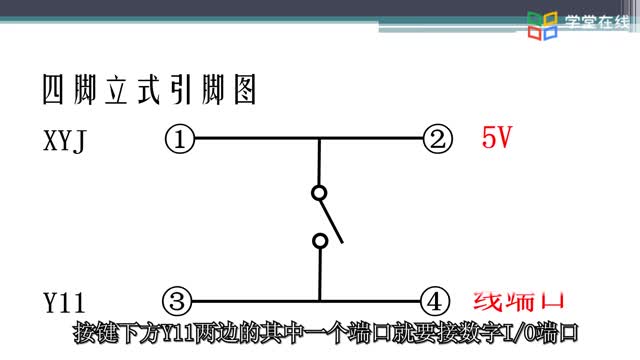

PORT(SW : IN std_logic_vector(3 DOWNTO 1);

L : OUT std_logic_vector(2 DOWNTO 1));

--L2 is a yellow LED AND L1 is a RED LED

END majority_voter;

--*********************************************

ARCHITECTURE concurrent OF majority_voter IS

BEGIN

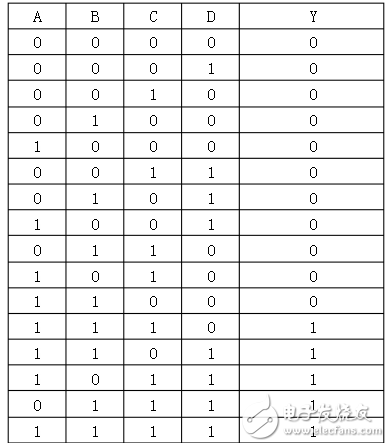

WITH SW SELECT

L <= "10" WHEN "011",

"10" WHEN "101",

"10" WHEN "110",

"10" WHEN "111",

"01" WHEN OTHERS;

END concurrent;

--*********************************************

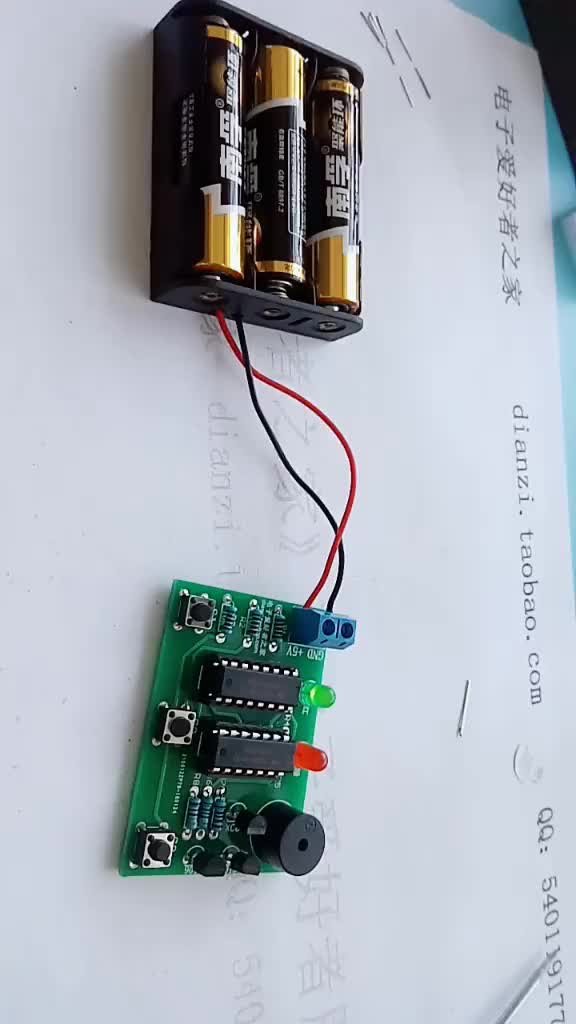

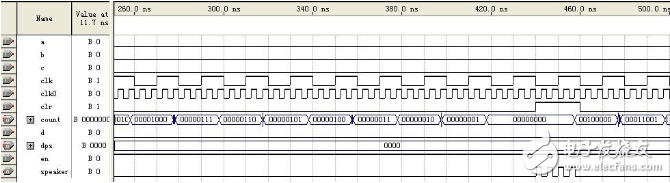

如下圖

電子發(fā)燒友App

電子發(fā)燒友App

評論