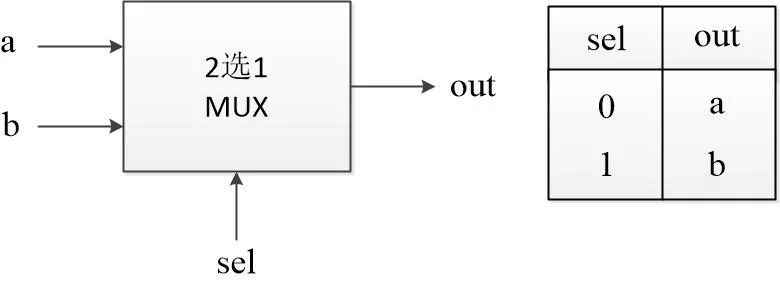

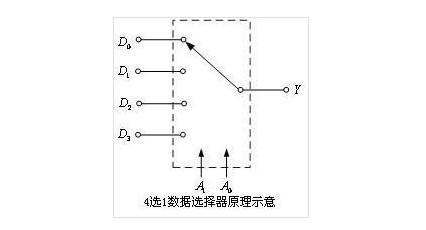

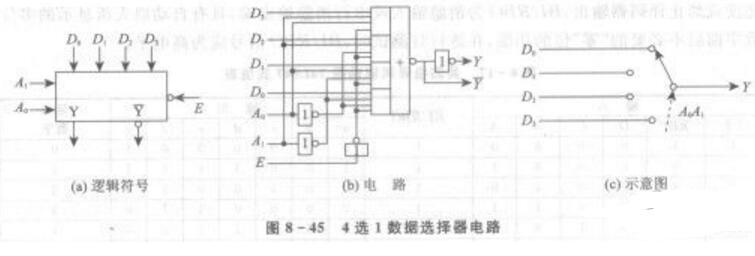

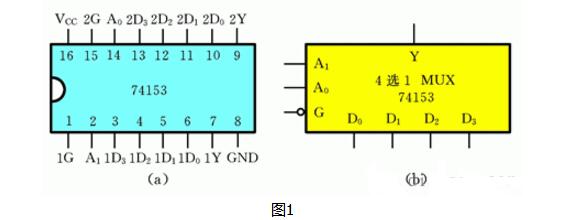

電子發(fā)燒友網(wǎng)核心提示:本例程是Verilog HDL源代碼:關于基本組合邏輯功能中多路選擇器(MUX)的功能實現(xiàn)源代碼。注意:程序運行在不同軟件平臺可能要作一些修改,請注意閱讀程序中的注釋。

//-----------------------------------------------------------------------------------

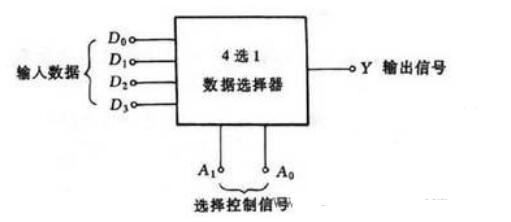

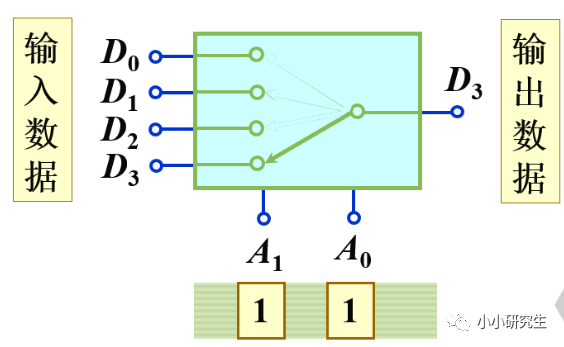

// DESCRIPTION?? :? Multiplexer

//??????????? Code style: used case statement

//????????????????? Width of output terminal: 8

//????????????????? Number of terminals: 4

//????????????????? Output enable active: HIGH

//????????????????? Output value of all bits when enable not active: 0

//-----------------------------------------------------------------------------------

module mux(EN ,IN0 ,IN1 ,IN2 ,IN3 ,SEL ,OUT );

input? EN ;

input? [7:0] IN0 ,IN1 ,IN2 ,IN3 ;

input? [1:0] SEL ;

output [7:0] OUT ;

reg? [7:0] OUT ;

always @(SEL? or EN? or IN0? or IN1? or IN2? or IN3 )

begin

if (EN? == 0) OUT? = {8{1'b0}};

else

case (SEL )

0 : OUT? = IN0 ;

1 : OUT? = IN1 ;

2 : OUT? = IN2 ;

3 : OUT? = IN3 ;

default : OUT? = {8{1'b0}};

endcase

end

endmodule

//-----------------------------------------------------------------------------------

// DESCRIPTION?? :? Multiplexer

//??????????? Code style: used case statement

//????????????????? Width of output terminal: 8

//????????????????? Number of terminals: 4

//????????????????? Output enable active: HIGH

//????????????????? Output value of all bits when enable not active: 0

//-----------------------------------------------------------------------------------

module mux(EN ,IN0 ,IN1 ,IN2 ,IN3 ,SEL ,OUT );

input? EN ;

input? [7:0] IN0 ,IN1 ,IN2 ,IN3 ;

input? [1:0] SEL ;

output [7:0] OUT ;

reg? [7:0] OUT ;

always @(SEL? or EN? or IN0? or IN1? or IN2? or IN3 )

begin

if (EN? == 0) OUT? = {8{1'b0}};

else

case (SEL )

0 : OUT? = IN0 ;

1 : OUT? = IN1 ;

2 : OUT? = IN2 ;

3 : OUT? = IN3 ;

default : OUT? = {8{1'b0}};

endcase

end

endmodule

電子發(fā)燒友App

電子發(fā)燒友App

評論