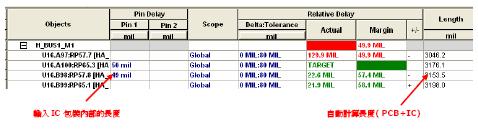

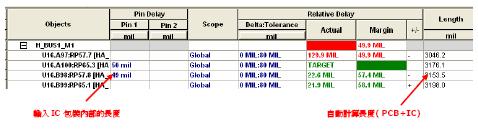

IC 包裝內(nèi)部的長(zhǎng)度計(jì)算 (pin delay)

在15.2, 新增pin property 來(lái)代表IC 包裝內(nèi)部的長(zhǎng)度, 您可以將IC 包裝內(nèi)部的長(zhǎng)度填入此字段, 并且

2009-09-06 11:22:46 4056

4056

顧名思義�����,output_delay就是指輸出端口的數(shù)據(jù)相對(duì)于參數(shù)時(shí)鐘邊沿的延時(shí)�。

2022-09-26 10:07:10 4831

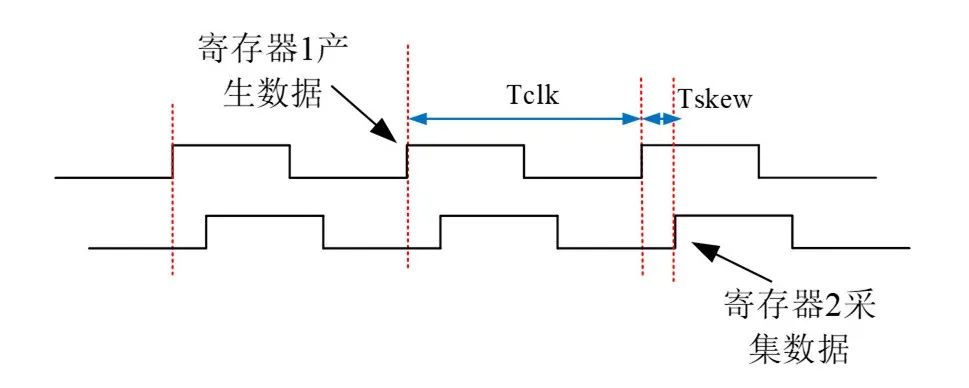

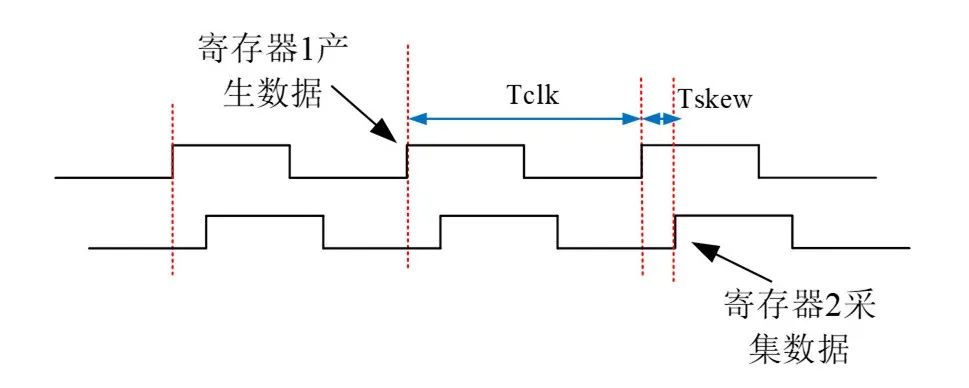

4831 針對(duì)第2章節(jié)時(shí)序路徑中用到skew,在本章再仔細(xì)講解一下�。

2023-08-14 17:50:58 2096

2096

在時(shí)序報(bào)告中�����,會(huì)顯示出clock path skew,如果時(shí)鐘偏移超過(guò)0.5ns���,就需要額外關(guān)注了�����。

2024-03-13 09:06:20 3009

3009

有客戶反饋DIsplayport HBR測(cè)試中Interpair skew的測(cè)量項(xiàng)目fail得比較異常��,就是固定的某條lane與其他lane之間的測(cè)試值不通過(guò)����,并且偏差很大�,都到幾十個(gè)UI了,并且固定在某個(gè)通道����,但是又沒(méi)有頭緒為什么。

2025-11-30 10:29:30 1365

1365

LI FE Battery study!!!!

2015-06-29 16:51:52

多年前,蘇格蘭愛(ài)丁堡大學(xué)移動(dòng)通信系教授哈羅德·哈斯提出一項(xiàng)理論���,稱可以利用LED燈傳輸數(shù)據(jù)?���,F(xiàn)在����,這項(xiàng)技術(shù)已經(jīng)在他的手上成為現(xiàn)實(shí)——成功研制出Li-Fi系統(tǒng)的工作原型。所謂的“Li-Fi”就是指

2016-01-20 10:11:11

and Correction (EDC)以外��,還有其他介紹總結(jié)“Memory Protection與Error Detection and Correction”功能的資料文檔嗎�?

2018-07-24 09:19:50

嗨,

我有一個(gè) Wemos D1 Mini ESP8266 模塊����,我正試圖通過(guò) MT3608 升壓模塊從 2400 mAh 鋰聚合物電池運(yùn)行。接線簡(jiǎn)單:

Li-Po正負(fù)極分別接MT3608的VIN+

2023-05-29 06:33:41

Gowin Color Correction Matrix IP用戶指南主要內(nèi)容包括功能描述���、端口描述�����、時(shí)序說(shuō)明�、配置調(diào)用、參考設(shè)計(jì)等�,旨在幫助用戶快速了解 GowinColor Correction Matrix IP 的產(chǎn)品特性、特點(diǎn)及使用方法���。

2022-10-08 06:02:14

Gowin Gamma Correction IP 用戶指南主要內(nèi)容包括概述�����、功能描述�����、端口描述�����、時(shí)序說(shuō)明����、配置調(diào)用�、參考設(shè)計(jì)等,旨在幫助用戶快速了解 GowinGamma Correction IP 的產(chǎn)品特性��、特點(diǎn)及使用方法。

2022-10-08 08:09:17

我們知道在RISC-V中有這樣一條偽指令:

li a0, immediately

可以將任意的32位數(shù)據(jù)或者地址加載到指定的寄存器中����,在 RV32I中,它擴(kuò)展到 lui 和/或 addi��。

li

2024-10-28 14:55:04

求助大神,clock skew太大����,導(dǎo)致時(shí)序違規(guī)怎么破?時(shí)鐘由DCM輸出��,已經(jīng)過(guò)BUFG

2016-01-14 17:00:12

我想使用本文中的Delay10MsTimes函數(shù)�,這里是HTTP://www. CyPress?ID=4和���;RID=47960。我解開(kāi)了DELAY.ASM和延遲.h文件��,并將它們包含在我的項(xiàng)目中���。我

2019-03-18 14:10:05

結(jié)構(gòu)緊湊的鋰(Li)電池充電器設(shè)計(jì)方案

2009-03-26 22:02:01

本帖最后由 一只耳朵怪 于 2018-6-22 10:47 編輯

各位專家大家好:我根據(jù) VPBE UG 的4.5.5.7 Gamma Correction RAM Table 對(duì)RAM 進(jìn)行

2018-06-22 02:44:50

(Skew)指標(biāo),但我目前沒(méi)在器件的數(shù)據(jù)手冊(cè)中查閱到這一指標(biāo)��,只能查閱到Aperture Delay這一參數(shù)���,如下圖:

請(qǐng)問(wèn)我應(yīng)該如何評(píng)估器件間的Aperture Delay Match這一特性���?

2023-12-01 06:17:55

The EL9115 is a triple analog delay line that allows skewcompensation between any three signals.

2009-01-16 08:56:16 16

16 The ISL59920 ia a triple analog delay line that provides skewcompensation between three high-speed

2009-01-17 20:59:17 24

24 Skew specifications are like any other ACelectrical specification. The measurementsare taken

2009-03-30 00:18:43 15

15 with zero delay and very low skew between the outputs. This device is well suited as a buffer for PCI or SDRAM due to its zero input to output dela

2009-05-27 13:48:00 64

64 蛇行線(delay tune)1. 前言蛇行線可在Allegro 中藉由elong_by_pick 自動(dòng)完成.若想以半自動(dòng)方式則可用delay tune 命令.2. 說明在15.1 中須下載新版ISR.Options 選項(xiàng)?

2009-09-06 11:30:35 0

0 Li-ion Battery Discharge Test Report:1. Li-ion battery dropout voltages test2. Li-ion battery

2009-11-20 14:55:09 16

16 Using Cycl

2009-11-27 13:55:25 15

15 Battery equalization using a plug-in charger in a hybrid electric vehicle

2009-11-28 11:56:35 11

11 Using Wavelet Eigenvalues as the Input of Pi-sigma Network to Recognize Movement Pattern

2010-02-22 11:38:01 13

13 Abstract:Nowadays new generation Power Factor Correction circuits based on "One-Cycle Control (OCC

2010-03-01 14:50:33 18

18 OB6561 is a cost effective high performancetransition-mode (TM) power-factor correction (PFC

2010-03-01 15:38:38 30

30 A New Three-Phase Power-Factor Correction (PFC) Scheme Using Two Single-Phase PFC Modules:Abstract

2010-03-01 17:42:23 36

36 This application report describes the process for using references to generate offsets forTexas Instrument’s TLC55XX family data converters.

2010-06-02 08:39:06 13

13 Using the

2010-08-22 12:34:56 18

18 Skew – Setup TimeHold Margin = Min Data Etch Delay – Max Clock Etch Del

2010-10-05 09:47:48 31

31 li ion是什么意思����?

鋰離子電池(Li-ion Batteries)是鋰電池發(fā)展而來(lái)。所以在介紹Li-ion之前��,先介紹鋰電池����。舉例來(lái)講,以前照相機(jī)里用的扣式電池就屬于鋰電

2008-02-24 14:51:05 37536

37536 Using the

2009-01-06 13:45:20 1045

1045

Display Backlighting Using High-Brightness LEDs and SEPIC Power Modules

Abstract:

2009-02-06 12:16:38 1234

1234

Using a UA

2009-03-31 22:18:45 2114

2114

12-Bit Thermometer Using an 8-Bit μC and Assembler

This application note explains how to implement

2009-03-31 22:25:39 951

951

Using the DS32kHz with Dallas Real-Time Clocks

Abstract: This application note describes how

2009-03-31 22:27:51 831

831 new-generation all-silicon delay lines. Both EconOscillators and delay lines use a compensated voltage-controlled delay line (VCDL) scheme to

2009-04-20 15:11:49 2565

2565

Abstract: Maxim manufactures several delay lines. This application note compares each programmable

2009-04-22 10:28:05 1390

1390

Using the

2009-04-23 08:42:35 1225

1225

Using a Ec

2009-04-23 10:31:26 1364

1364

Using Maxi

2009-04-26 16:32:40 1174

1174

Using Maxi

2009-04-27 09:50:06 1565

1565

Abstract: Maxim manufactures several delay lines. This application note compares each programmable

2009-04-29 09:56:33 3310

3310

Abstract: This application note presents to the reader a recommended Li-Ion battery pack circuit

2009-04-30 14:18:57 1478

1478

Battery Backup with Delay(具有時(shí)滯的備用電池)

Abstract: This application note explains

2009-07-29 10:00:49 1943

1943

Using the Serial Port on the MAXQ610 Microcontroller

Abstract: The MAXQ610 microcontroller

2009-08-13 12:05:56 1525

1525 什么是Li-ion電池

Li-ion是鋰電池發(fā)展而來(lái)����。所以在介紹Li-ion之前�,先介紹鋰電池���。舉例來(lái)講����,以前照相機(jī)里用的扣式電池就屬于鋰電池

2009-11-04 16:43:12 5259

5259 Li-ion電池有哪些優(yōu)點(diǎn)��?哪些缺點(diǎn)����?

Li-ion具有以下優(yōu)點(diǎn):

1) 單體電池的工作電壓高達(dá)3.6-3.8V:

2009-11-04 16:45:47 4829

4829 金屬鋰(Li)的簡(jiǎn)介

元素符號(hào):Li。銀白色的金屬���。密度0.534克/厘米3�。熔點(diǎn)180.54℃���。沸點(diǎn)1317℃。是最輕的金屬?�?膳c大量無(wú)機(jī)試劑和有

2009-12-01 09:29:09 15757

15757 簡(jiǎn)化Li電池充電器設(shè)計(jì)

鋰離子(Li+)電池比其它化學(xué)類型的電池

2009-12-08 10:49:34 838

838 Propagation Delay Measurements Using TDR (Time-Domain Reflectometry)

Abstract: As clock speeds

2010-02-21 09:48:00 3532

3532

The ADP1047/ADP1048 are digital power factor correction (PFC) controllers that provide accurate

2011-11-26 14:21:32 29

29 本文詳細(xì)討論了VHDL語(yǔ)句對(duì)PLD設(shè)計(jì)的影響和設(shè)計(jì)經(jīng)驗(yàn)�����,經(jīng)典文章��,值得仔細(xì)閱讀消化�。, PLD Programming Using VHDL

2012-01-17 11:20:54 0

0 Linux之work_queue_delay_work教程,很好的Linux自學(xué)資料��,快來(lái)學(xué)習(xí)吧��。

2016-04-15 17:54:28 12

12 (ebook) Chu - FPGA Prototyping Using Verilog Examples

2016-06-03 16:16:53 14

14 Free RTOS Book Using the FreeRTOS Real Time Kernel - A Practical Guide - NXP LPC17xx Edition

2016-07-13 15:11:08 30

30 也許你只聽(tīng)過(guò)Wi-Fi��,卻未曾聽(tīng)過(guò)Li-Fi���。所以��,本文旨在帶大家走近 Li-Fi 技術(shù)這一創(chuàng)新智慧����,從多個(gè)方面包括原理�����、發(fā)明者、發(fā)展歷程���、特點(diǎn)和優(yōu)勢(shì)�����、應(yīng)用前景���、商用和測(cè)試等等,進(jìn)行觀察和剖析�����,讓大家全方位地理解 Li-Fi 技術(shù)���。

2016-12-21 15:21:12 6872

6872 Dc綜合是基于路徑�����,每個(gè)路徑上都有Cell和net�,所以基于路徑的綜合就是計(jì)算路徑上的delay和rc(dc是使用互連線模型進(jìn)行估算)���。

2018-07-15 09:03:00 16947

16947

什么叫DCM(Digital Clock Management)? DCM內(nèi)部是DLL(Delay Lock Loop(?)結(jié)構(gòu),對(duì)時(shí)鐘偏移量的調(diào)節(jié)是通過(guò)長(zhǎng)的延時(shí)線形成的�����。DCM的參數(shù)里有一個(gè)PHASESHIFT(相移),可以從0變到255���。

2018-07-15 11:28:00 6076

6076 對(duì)于positive skew來(lái)說(shuō),它可以減少T的時(shí)間�����,相當(dāng)于提升芯片的performace�����。但是它的hold時(shí)間會(huì)變得更加難以滿足對(duì)于negative skew來(lái)說(shuō)����,它的hold時(shí)間更加容易滿足,取而代之的是����,它會(huì)降低芯片的性能�。

2018-07-23 17:15:19 19138

19138

芯片延遲Delay測(cè)試的學(xué)習(xí)課件PDF文件免費(fèi)下載包括了:? 為什么需要Delay測(cè)試 ? Delay產(chǎn)生原因和缺陷機(jī)制 ? Delay故障建模 ? Delay故障仿真 ? Delay故障ATPG ? Delay測(cè)試結(jié)構(gòu)和ATPG商用工具

2020-12-01 08:00:00 5

5 LTC6994: Delay

2021-02-03 16:39:33 3

3 Efficient packet classification using TCAM(現(xiàn)代電源技術(shù)基礎(chǔ)課程)-Efficient packet classification using TCAM

2021-08-04 16:23:04 14

14 使用st-li

2021-11-17 09:21:04 7

7 硬件連接引腳定義:ST-li

2021-11-20 12:36:02 8

8 以下解釋以stm32f4為例子1�、ST-li

2021-11-24 17:51:06 9

9 利用ST-li

2021-11-24 18:36:05 17

17 STM32之ST-li

2021-11-24 18:36:06 35

35 delay.h/* --------------------------------------------------------- */// 文件名稱:delay.h // 功能描述

2021-11-24 19:06:02 13

13 目錄1、關(guān)于e-li

2021-12-02 20:06:07 6

6 一��、環(huán)境1.J-li

2021-12-03 13:36:01 0

0 添加鏈接描述JTAG是調(diào)試接口協(xié)議J-li

2021-12-03 14:51:09 11

11 1.J-li

2021-12-05 12:06:15 0

0 正版ST-li

2021-12-07 14:36:12 0

0 關(guān)注�����、星標(biāo)公眾號(hào)����,不錯(cuò)過(guò)精彩內(nèi)容作者:strongerHuang微信公眾號(hào):strongerHuangST-li

2021-12-07 19:21:11 9

9 一、工具1��、J-li

2021-12-08 16:21:07 0

0 stm32 delay文件總結(jié)delay.h#ifndef __DELAY_H#define __DELAY_H #include "sys.h" void delay

2021-12-24 19:36:36 6

6 1����、使用SYStick專門(mén)的延時(shí)。void delay_us(uint32_t us){ static uint32_t delay_flag = 0; delay_flag = 1; /* set

2021-12-24 19:39:28 2

2 在STA中�����,要分析上游器件和FPGA之間的時(shí)序關(guān)系就得指定input delay����。

2022-02-19 19:32:16 4317

4317

本文章探討一下FPGA的時(shí)序input delay約束���,本文章內(nèi)容,來(lái)源于配置的明德?lián)P時(shí)序約束專題課視頻���。

2022-05-11 10:07:56 4989

4989

本文章探討一下FPGA的時(shí)序input delay約束,本文章內(nèi)容�,來(lái)源于明德?lián)P時(shí)序約束專題課視頻。

2022-07-25 15:37:07 3758

3758

電子發(fā)燒友網(wǎng)站提供《Gowin Gamma Correction IP用戶指南.pdf》資料免費(fèi)下載

2022-09-15 15:13:55 2

2 Gowin Color Correction Matrix IP 用戶指南主要內(nèi)容包括功能描述���、端

口描述��、時(shí)序說(shuō)明��、配置調(diào)用���、參考設(shè)計(jì)等,旨在幫助用戶快速了解 Gowin

Color Correction Matrix IP 的產(chǎn)品特性����、特點(diǎn)及使用方法。

2022-09-15 14:26:43 0

0 為了更容易看到工具做的useful skew的效果���,這里故意在下面的path上設(shè)置了很大(2.5ns)的path margin���,這里是在Place階段啟用的CCD��。

2022-09-30 15:57:29 3874

3874 IP_數(shù)據(jù)表(A-6):Analog-PLL For Skew adjust

2023-03-16 19:27:43 0

0 IP_數(shù)據(jù)表(A-9):Analog-PLL For Skew adjust

2023-03-16 19:28:21 0

0 Incr Delay是由于SI信號(hào)完整性(比如cross talk��、電磁等)造成的增量延時(shí)�,也稱為噪聲延遲(incr delay)���。

2023-04-03 10:54:32 4916

4916 本文將介紹SysTick與HAL_Delay()函數(shù)之間的關(guān)系����,以及使用HAL_Delay()函數(shù)的注意事項(xiàng)��;

2023-04-21 11:32:11 3353

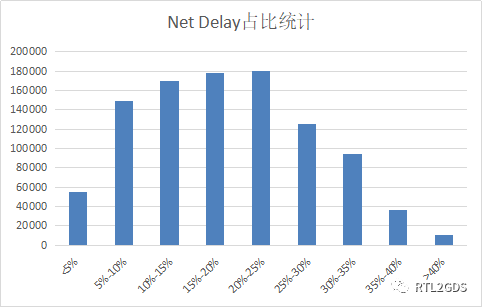

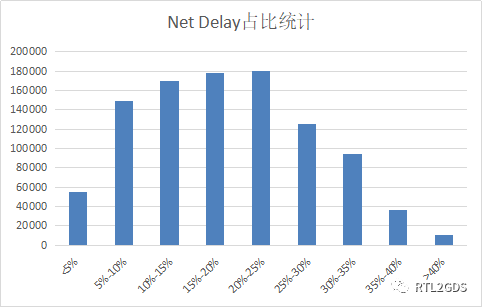

3353 繞線延時(shí)(Net Delay)是怎么計(jì)算出來(lái)的呢?Net Delay在整個(gè)路徑延時(shí)(Path Delay)的占比又是什么情況呢����?針對(duì)關(guān)鍵路徑,工具會(huì)如何降低Net Delay呢?下面我們就來(lái)逐步闡述�。

2023-06-27 14:07:41 3710

3710

今天要介紹的時(shí)序分析基本概念是skew,我們稱為偏差�。

2023-07-05 10:29:37 5173

5173

IP_數(shù)據(jù)表(A-6):Analog-PLL For Skew adjust

2023-07-06 20:14:06 0

0 IP_數(shù)據(jù)表(A-9):Analog-PLL For Skew adjust

2023-07-06 20:14:39 0

0 \n");HAL_Delay(1000);}}voidB(void*argument){while(1){printf("B\r\n");HAL_Delay(1000);}}燒

2023-10-29 08:00:52 4718

4718

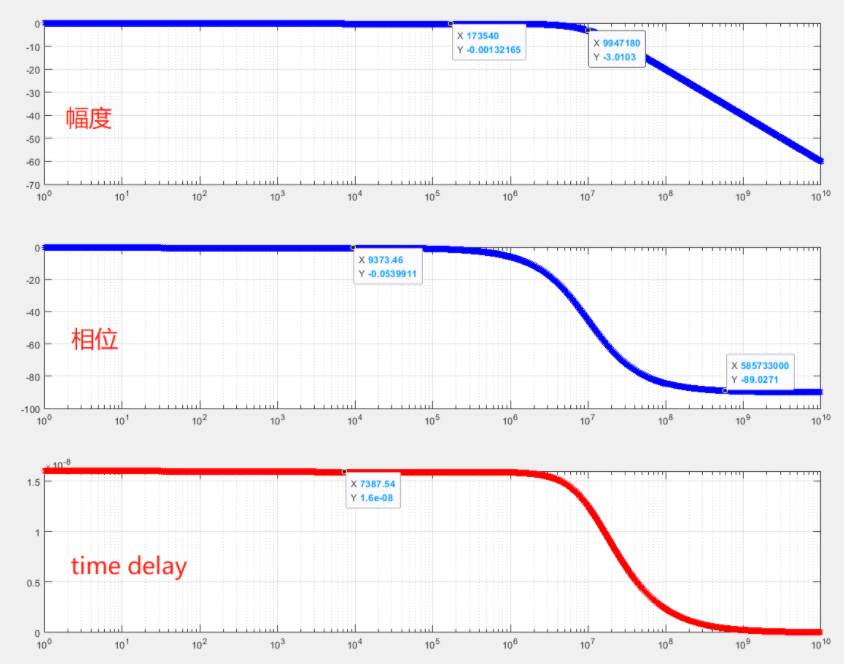

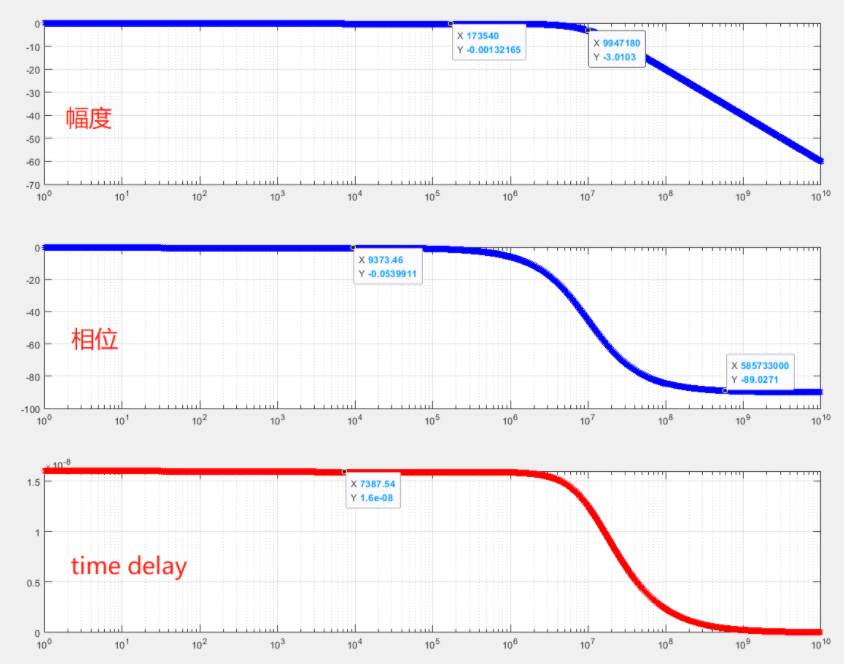

假設(shè)信號(hào)經(jīng)過(guò)一階低通濾波器(-3dB帶寬為f0),那在所有頻率點(diǎn)����,信號(hào)的delay是怎樣的?

tao=16ns時(shí)�����,我用matlab plot了一下幅度�����、相位和time delay���,其中time delay=phase/w (其中w為角頻率,phase量綱為rad/s)

2023-11-29 15:04:43 3273

3273

前言 本次的文章來(lái)源于Samtec首席技術(shù)專家兼總監(jiān)布蘭登?戈?duì)枺˙randon Gore)博士對(duì)線纜Skew的一次深入分享探討。 我們截取了部分討論的重點(diǎn)內(nèi)容�����。一如既往���,分享給大家�����,希望拋磚引玉

2025-04-14 14:11:34 803

803

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論