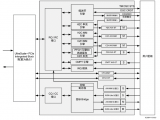

本視頻介紹了使用處理子系統(tǒng)中的PCI Express模塊創(chuàng)建Zynq UltraScale +解決方案的過程。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

PCI

+關(guān)注

關(guān)注

5文章

689瀏覽量

134286 -

Zynq

+關(guān)注

關(guān)注

10文章

630瀏覽量

49468

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

MAX5954:PCI Express熱插拔控制器的卓越之選

MAX5954:PCI Express熱插拔控制器的卓越之選 在PCI Express應(yīng)用領(lǐng)域,熱插拔控制器的性能直接影響著系統(tǒng)的穩(wěn)定性和可靠性。今天我們要深入探討的是Maxim

MAX5946:雙PCI Express熱插拔控制器的全方位解析

MAX5946:雙PCI Express熱插拔控制器的全方位解析 在PCI Express應(yīng)用領(lǐng)域,熱插拔功能至關(guān)重要,它能在系統(tǒng)運行時安全地插入或移除設(shè)備,提高系統(tǒng)的可維護性和靈活性

LTC4242:PCI Express熱插拔控制器的卓越之選

LTC4242:PCI Express熱插拔控制器的卓越之選 在PCI Express系統(tǒng)的設(shè)計中,熱插拔功能至關(guān)重要,它能實現(xiàn)設(shè)備的在線插入和移除,提高系統(tǒng)的可用性和可維護性。LTC

PI7C9X110:PCI Express到PCI可逆橋接器的技術(shù)剖析與應(yīng)用指南

PI7C9X110:PCI Express到PCI可逆橋接器的技術(shù)剖析與應(yīng)用指南 在當(dāng)今的電子科技領(lǐng)域,PCI Express和

使用Aurora 6466b協(xié)議實現(xiàn)AMD UltraScale+ FPGA與AMD Versal自適應(yīng)SoC的對接

在本博客中,我們將介紹使用 Aurora 6466b 協(xié)議實現(xiàn) AMD UltraScale+ FPGA 與 AMD Versal 自適應(yīng) SoC 的對接。我們還將涵蓋有關(guān) IP 配置、FPGA 之間的連接、時鐘設(shè)置以及復(fù)位拓撲結(jié)構(gòu)的詳細信息。

如何在Zynq UltraScale+ MPSoC平臺上通過JTAG啟動嵌入式Linux鏡像

流程教程)。本文則進一步講解如何在 Zynq UltraScale+ MPSoC 平臺上通過 JTAG 逐步啟動 Linux,并提供了完整的過程與關(guān)鍵命令。只要按步驟操作,即使是復(fù)雜的 Linux 鏡像也能成功通過 JTAG 啟

深入剖析DS50PCI401:PCI Express應(yīng)用的理想選擇

深入剖析DS50PCI401:PCI Express應(yīng)用的理想選擇 在PCI Express應(yīng)用的領(lǐng)域中,DS50

探索DS50PCI402:PCI Express應(yīng)用的理想選擇

探索DS50PCI402:PCI Express應(yīng)用的理想選擇 在PCI Express應(yīng)用領(lǐng)域,找到一款性能卓越、功能豐富且易于配置的設(shè)備

探索DS80PCI402:PCI - Express中繼器的卓越性能與應(yīng)用實踐

探索DS80PCI402:PCI - Express中繼器的卓越性能與應(yīng)用實踐 在當(dāng)今高速發(fā)展的電子科技領(lǐng)域,PCI - Express(P

AMD Spartan UltraScale+ FPGA的優(yōu)勢和亮點

AMD Spartan UltraScale+ FPGA 集小型封裝、先進的 I/O 功能與低功耗等優(yōu)勢于一體。該系列 FPGA 配備高速 16.3 Gb/s 收發(fā)器、內(nèi)置的外部內(nèi)存控制器以及

璞致電子 UltraScale+ RFSoC 架構(gòu)下的軟件無線電旗艦開發(fā)平臺

璞致電子 PZ-ZU49DR-KFB 開發(fā)板基于 Xilinx ZYNQ UltraScale+ RFSoC XCZU49DR 主控制器,以 "ARM+FPGA 異構(gòu)架構(gòu)" 為

AMD Spartan UltraScale+ FPGA 開始量產(chǎn)出貨

高 I/O、低功耗及先進的安全功能,適用于成本敏感型邊緣應(yīng)用 AMD 很高興宣布,Spartan UltraScale+ 成本優(yōu)化型系列的首批器件現(xiàn)已投入量產(chǎn)! 三款最小型的器件——SU10P

QDMA Subsystem for PCI Express v5.0產(chǎn)品指南

AMD QDMA Subsystem for PCI Express( PCIe )旨在利用多隊列的概念實現(xiàn)高性能 DMA,以搭配 PCI Express Integrated Blo

Xilinx Ultrascale系列FPGA的時鐘資源與架構(gòu)解析

。Ultrascale+采用16ns,有3個系列:Artix,Kintex,Virtex。不僅是工藝制程方面,在其他方面也存在較大改進,如時鐘資源與架構(gòu),本文將重點介紹Ultrascale的時鐘資源與架構(gòu),

使用PCI Express模塊??創(chuàng)建Zynq UltraScale+的過程介紹

使用PCI Express模塊??創(chuàng)建Zynq UltraScale+的過程介紹

評論