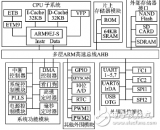

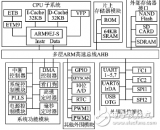

多片F(xiàn)PGA之間的互連���,經(jīng)常提到多路復(fù)用的概念���,也經(jīng)常提到TDM的概念,正確理解多路復(fù)用在多片F(xiàn)PGA原型驗證系統(tǒng)中的機理����,尤其是時序機制,對于我們正確看待和理解多片F(xiàn)PGA原型系統(tǒng)的性能有很好的促進作用���。下圖是一個使用多路復(fù)用器后接采樣FF的多路復(fù)用解決方案的示例����。

2023-06-06 10:04:35 579

579

描述該設(shè)計適用于針對直流輸入的 16 位 1MSPS 單端多路復(fù)用數(shù)據(jù)采集系統(tǒng) (DAQ)。該系統(tǒng)包含一個 16 位逐次逼近型寄存器 (SAR) 模數(shù)轉(zhuǎn)換器 (ADC)���、一個 SAR ADC 驅(qū)動器

2018-11-07 14:48:51

多路tcp通信和tcp多路復(fù)用一樣嗎 我找不到多路tcp通信的資料??

2018-03-21 10:35:12

想要一個外部多路復(fù)用器��,例如TS3A24159���,從串行端口切換到PGED1和PGEC1�����。問題是如何控制開關(guān)����。由于MCLR通常保持在3.3V�����,并且當程序員連接到13V時,我想添加一個分壓器�,具有全局電阻

2020-04-01 08:19:03

總線多路復(fù)用器LTC4305資料下載內(nèi)容包括:LTC4305引腳功能LTC4305內(nèi)部方框LTC4305典型應(yīng)用電路LTC4305電氣參數(shù)

2021-03-23 07:50:25

),單位是MB/S�����;總線傳輸速率=(總線寬度÷8位)×總線頻率BW=(w÷8) × f總線的其他性能指標:同步方式:同步�,異步多路復(fù)用:地址總線和數(shù)據(jù)線能否公用一條物理線;信號線數(shù)量:數(shù)...

2022-03-01 06:43:11

FPGA設(shè)計����,外部時鐘有兩個,切換時可以用多路復(fù)用開關(guān)實現(xiàn)嗎

2020-06-27 22:17:51

AD8174-EB�,用于視頻路由和多路復(fù)用系統(tǒng)的單路4:1模擬多路復(fù)用器評估板。 AD8174評估板經(jīng)過精心布局和測試�����,可演示器件的指定高速性能

2020-06-17 09:58:16

AD8183-EVAL���,用于視頻路由和多路復(fù)用系統(tǒng)的三路2:1模擬多路復(fù)用器評估板�����。 AD8183評估板經(jīng)過精心布局和測試����,以展示器件的指定高速性能

2020-06-17 12:40:57

AD8184-EB,用于視頻路由和多路復(fù)用系統(tǒng)的單路4:1模擬多路復(fù)用器評估板��。 AD8184評估板經(jīng)過精心布局和測試��,可演示器件的指定高速性能

2020-06-17 06:28:31

AD8185-EVAL�,用于視頻路由和多路復(fù)用系統(tǒng)的三路2:1模擬多路復(fù)用器評估板。 AD8185評估板經(jīng)過精心布局和測試����,以展示器件的指定高速性能

2020-06-17 16:47:30

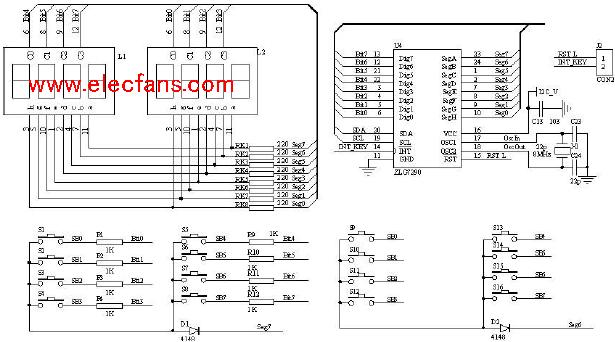

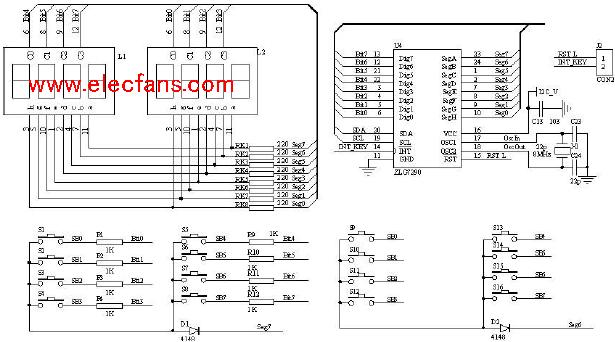

I2C 總線接口的實時時鐘/日歷芯片

2023-03-28 12:56:59

你好�����,根據(jù)技術(shù)參考手冊����,CY7C64 xx EnCOREV設(shè)備具有全設(shè)備的模擬I/O多路復(fù)用總線。有可能使用這個總線重新映射GPIO引腳嗎����?例如,我想重新映射P1Y6(TimeRoT)到P1Y7���,以

2019-05-07 07:51:26

電池���。(特權(quán)同學�����,版權(quán)所有)圖3.76 實時時鐘接口電路U2的各個引腳定義如表3.13所示���。(特權(quán)同學,版權(quán)所有)表3.13 實時時鐘芯片的引腳定義引腳信號功能1OSCI32.768KHz晶體輸入引腳

2015-06-05 12:19:43

PCF8563P��,雙列貼片8腳封裝�����。是低功耗的CMOS實時時鐘日歷芯片它提供一個可編程時鐘輸出一個中斷輸出和掉電檢測器所有的地址和數(shù)據(jù)通過I2C總線接口串行傳遞最大總線速度為400Kbits/s�����。每次讀寫數(shù)據(jù)后

2021-04-28 07:04:25

PCF8563T是荷蘭皇家飛利浦公司生產(chǎn)的芯片�,雙列貼片8腳封裝。是低功耗的CMOS實時時鐘日歷芯片它提供一個可編程時鐘輸出一個中斷輸出和掉電檢測器所有的地址和數(shù)據(jù)通過I2C總線接口串行傳遞最大總線

2021-04-16 07:38:21

�。而且,它不象ISA總線那樣把地址尋址和數(shù)據(jù)讀寫控制信號都交給微處理器來處理�,而是獨立于處理器�,所以它可以支持突發(fā)傳送��。PCI總線與CPU無關(guān)����,與時鐘頻率也無關(guān),因此它可以應(yīng)用于各種平臺�,支持多處理器

2018-11-29 14:52:52

2.2版本PCI規(guī)范。PCI9054本地總線支持非多路復(fù)用32位地址/數(shù)據(jù)總線�,多路復(fù)用32位和8位,16位或32位本地總線設(shè)備從屬訪問�����,運行速率高達50MHz���,可以獲得200MB/S的本地總線突發(fā)傳輸

2008-10-09 11:23:38

速率達到132MB/s,本地總線支持復(fù)用/非復(fù)用的32位地址/數(shù)據(jù)���;有M���、C、J三種模式��;針對不同的處理器及局總線特性可選,盡量減少中間邏輯���;具有可選的串行EEPROM接口�,本地總線時鐘可和PCI時鐘

2018-12-05 10:12:42

實時時鐘模塊(I2C總線)

2023-03-28 18:26:06

實時時鐘模塊(I2C總線)

2023-03-24 14:48:54

多路復(fù)用器不兼容(“在硬件系統(tǒng)中找不到可用的閃存控制器��?�!保?���。我應(yīng)該將閃存與另一個內(nèi)存控制器核心連接嗎?任何提示是開始解決這個問題���?我認為它必須簡單����,很多人使用這個板��,應(yīng)用程序需要外部RAM����,程序存儲器和引導加載。謝謝�����,本斯

2019-09-17 09:54:43

的時間和日期RTC由兩個主要部分組成�。第一部分(APB1接口)用來和APB1總線相連。此單元還包含一組16位寄存器����,可通過APB1總線對其進行讀寫操作。APB1接口以APB1總線時鐘為時鐘�。另一部分(...

2022-01-26 07:53:26

工作2.其它特點·具有與處理器和存儲器子系統(tǒng)完全并行操作的能力 ·具有隱含的中央仲裁系統(tǒng) ·采用多路復(fù)用方式(地址線和數(shù)據(jù)線)減少了引腳數(shù)·支持64位尋址 ·完全的多總線主控能力 ·提供地址和數(shù)據(jù)

2008-12-09 13:46:13

RTC實時時鐘IC:FH8563(內(nèi)置64字節(jié)RAM、32K輸出�、時鐘精度調(diào)整寄存器)■器件概述FH8563是一種具有標準IIC接口的實時時鐘芯片,CPU可使用該接口通過6位地址尋址來讀寫片內(nèi)64

2022-01-21 21:52:01

�����,完成一次總線( 讀寫) 操作周期為T�����,P0 口分時復(fù)用�����,在T0 期間�,P0 口送出低8 位地址,在ALE 的下降沿完成數(shù)據(jù)鎖存���,送出低8位地址信號���。在T1 期間,P0 口作為數(shù)據(jù)總線使用���,送出或讀入數(shù)據(jù)

2018-07-28 20:56:47

����,完成一次總線( 讀寫) 操作周期為T,P0 口分時復(fù)用��,在T0 期間����,P0 口送出低8 位地址,在ALE 的下降沿完成數(shù)據(jù)鎖存�,送出低8位地址信號。在T1 期間,P0 口作為數(shù)據(jù)總線使用�,送出或讀入數(shù)據(jù)

2018-07-24 17:02:41

擬多路復(fù)用器和開關(guān)的原理是什么����?如何設(shè)計出模擬多路復(fù)用器和開關(guān)解決方案

2021-03-11 07:46:19

新功能包括拆分事務(wù),單周期總線主控切換�,單時鐘沿操作以及更寬的數(shù)據(jù)總線配置(即64/128位)。AHB必須包含主機和從機之外的許多組件�。這些組件是地址和控制多路復(fù)用器,讀取多路復(fù)用器���,寫入多路復(fù)用

2020-09-28 10:16:11

圖1:具有8:1多路復(fù)用器的通用輸入/輸出(GPIO)擴展功能幸運的是�,小尺寸的8:1多路復(fù)用器可提供相對簡單的解決方案�,如TMUX1308。當你想到小尺寸多路復(fù)用器時��,可能會認為唯一的選擇

2022-11-07 07:07:43

LTC4312的典型應(yīng)用是可熱插拔的2通道2線總線多路復(fù)用器,允許一個上游總線連接到下游總線或通道的任意組合

2019-05-09 08:12:11

和一個單獨地址(取決于 ID)�。這是在多路復(fù)用器的幫助下完成的,在初始化之后���,多路復(fù)用器始終被設(shè)置���,以便所有 STM32g0 都連接到 I2C 總線。目前�,控制器發(fā)送一條命令,表示它將請求分別向每個

2022-12-08 08:09:27

NuMicro? M05xxBN/DN/DE 系列配備一個外部總線接口 (EBI) , 用來訪問外部設(shè)備.

為節(jié)省外部設(shè)備與芯片的連接引腳數(shù)�, EBI支持地址總線與數(shù)據(jù)總線復(fù)用模式. 且地址鎖存使能

2023-06-16 06:41:36

我正在移植一個草圖(我需要將其轉(zhuǎn)換為一個庫)�,用于將 14 段顯示器(六個字符�����,但可以擴展)從 Arduino 驅(qū)動到 ESP-01��。

我試圖找出驅(qū)動多路復(fù)用的最佳方法�。我把硬件都整理

2023-05-24 07:05:59

我們正在研究 FlexCAN1 的 mxrt1051�����。我們是第一次在 FlexCAN 上工作,請協(xié)助以下幾點:

- 如何在 Mx1051 的 FlexCAN1 中配置簡單信號多路復(fù)用和擴展信號

2023-05-05 11:05:58

�,但我似乎在 SPI SCLK 線上獲得大約 12 MHz 到 16 MHz 的頻率以進行 QSPI 快速讀取。我能在這里錯過什么�?我已經(jīng)檢查了我的寄存器設(shè)置,以仔細檢查 FLEXSPI 塊的多路復(fù)用器和分頻器設(shè)置是否有效�����。我正在使用 FLEXSPI 阻塞讀取功能來執(zhí)行與 NOR 閃存設(shè)備的傳輸

2023-03-29 06:19:53

嗨�,我嘗試使用KC705來實現(xiàn)以下時鐘Mux功能。CLK_P / CLK_N是KC705 200MHz參考時鐘����。但它總是報告FPGA實現(xiàn)過程中的錯誤。 “BUFG級聯(lián)錯誤”�。您想給我一些建議如何通過KC705實現(xiàn)以下時鐘多路復(fù)用功能嗎?謝謝��,可能

2020-07-21 14:27:42

����,提供ADC和數(shù)字主機之間高達300 MHz(CLK±和D±)的高速數(shù)據(jù)傳輸���。 LVDS接口允許多個器件共享時鐘���,從而降低數(shù)字線路的數(shù)量�����,并簡化信號路由�。 相比并行接口它具有更低的功耗�,因此在多路復(fù)用

2019-10-23 08:30:00

1模擬開關(guān)和多路復(fù)用器有哪些新的功能? 模擬開關(guān)和多路復(fù)用器正在擴展它們的應(yīng)用范圍�,從工業(yè)和儀器儀表設(shè)備、通信基礎(chǔ)設(shè)施到消費類電子設(shè)備(例如音視頻接收機和手機�����,它們都需要靈活的帶寬和信號幅度

2011-10-13 15:39:48

)74HC4052D,653接口 - 模擬開關(guān),多路復(fù)用器�,多路分解器資料PDF/SGS安逸通國際有限公司地址:香港九龍旺角西海富菀海欣閣2804(HK)電話:00852- 39904203(HK)傳真

2012-05-15 20:45:18

本帖最后由 eehome 于 2013-1-5 10:10 編輯

各位前輩大家好,本人想請教一下各位十六位地址總線和數(shù)據(jù)總線的數(shù)據(jù)讀和寫使用什么設(shè)備?��?�?希望能給推薦一個�����,最好是我可以選擇讀寫地址范圍的�。謝謝���!

2012-08-28 10:31:43

領(lǐng)域�。本文基于雷達實時信號處理的需要�,用FPGA實現(xiàn)了多DSP信號處理模板局部總線和基于標準VME總線的計算機進行通信的接口設(shè)計。 2 VME總線的功能特點VME總線系統(tǒng)的功能結(jié)構(gòu)可以分為4類:數(shù)據(jù)

2019-04-22 07:00:07

AD8170-EB���,用于視頻路由和多路復(fù)用系統(tǒng)的單路2:1模擬多路復(fù)用器評估板�。 AD8170評估板經(jīng)過精心布局和測試���,可演示器件的指定高速性能

2020-06-17 16:47:30

電源復(fù)用器電源多路復(fù)用器(Power MUX)是一組電子開關(guān)�����,用于選擇兩個或更多輸入功率路徑并轉(zhuǎn)換到單個輸出��。目的旨在靈活地在不同類型的輸入電源(桶式插孔�,USB電纜,無線充電)之間進行選擇的系統(tǒng)

2021-10-29 09:16:05

總線中為了優(yōu)化設(shè)計采用了地址線和數(shù)據(jù)線共用一組物理線路���,即多路復(fù)用。PCI接插件尺寸小���,又采用了多路復(fù)用技術(shù)����,減少了元件和管腳個數(shù)��,提高了效率����。(9)嚴格規(guī)范PCI總線對協(xié)議、時序���、電氣性能�、機械性能等

2018-02-06 09:50:28

1�、組合邏輯基礎(chǔ)之多路復(fù)用器設(shè)計多路復(fù)用器也叫數(shù)據(jù)選擇器,如下圖所示����,是根據(jù)選擇信號Sel的值從多個數(shù)據(jù)輸入中選擇其中一個進行輸出�����,是數(shù)字系統(tǒng)中應(yīng)用非常廣泛的一種邏輯電路���。如下是一個典型的四選一多路復(fù)用

2022-08-04 17:06:09

PCF8563是經(jīng)典低功耗實時時鐘/日歷芯片[4]����,具有IIC總線接口技術(shù),總線最大傳輸速度可達400 kb/s�,每次寫讀數(shù)據(jù)后,內(nèi)部包含的字地址寄存器就會自動遞增����,具有功耗低�����、精度高等特點�����。PCF8563

2019-06-20 05:00:04

高通道密度數(shù)據(jù)采集系統(tǒng)用于醫(yī)療成像��、工業(yè)過程控制���、自動測試設(shè)備和40G/100G光通信系統(tǒng)可將眾多傳感器的信號多路復(fù)用至少量ADC�����,隨后依序轉(zhuǎn)換每一通道��。 多路復(fù)用可讓每個系統(tǒng)使用更少的ADC�,大幅

2020-12-21 06:11:56

多路復(fù)用與數(shù)字復(fù)接8.1 頻分多路復(fù)用(FDM)原理8.2 時分多路復(fù)用(TDM)原理8.3 準同步數(shù)字體系(PDH) 8.4 同步數(shù)字體系(SDH)

2008-10-22 13:26:58 0

0 PCF8563 是低功耗的CMOS 實時時鐘日歷芯片.它提供一個可編程時鐘輸出一個中斷輸出和掉電檢測器.所有的地址和數(shù)據(jù)通過I2C 總線接口串行傳遞最大總線速度為400Kbits/s 每次讀寫數(shù)據(jù)后

2009-01-12 13:01:58 80

80 MSM6242B 直接總線連接的CMOS實時時鐘,日歷的典型應(yīng)用和應(yīng)用筆記

2009-05-19 16:57:48 18

18 2.3 多路復(fù)用技術(shù)2.3.1 頻分多路復(fù)用2.3.2 時分多路復(fù)用2.3.3 波分多路復(fù)用2.3.4 碼分多路復(fù)用2.3.1 頻分多路復(fù)用2.3.1 頻分多路復(fù)用&nb

2009-06-27 21:46:04 0

0 PCA9546A 是一款I(lǐng)2C 多路復(fù)用器和開關(guān)����,能實現(xiàn)I2C 總線擴展、電平轉(zhuǎn)換及總線功能恢復(fù)

2009-11-11 11:45:04 36

36 PCA9544A 是NXP 公司生產(chǎn)的I2C 總線多路復(fù)用器�����,通過該器件可以將一路I2C 總線擴展為4 路I2C 總線。將1 路上行SDA/SCL 通道擴展為4 路下行通道���。通過對內(nèi)部可編程寄存器進行配置

2009-11-11 11:56:14 20

20 一�、物料概述PCF8563是一款CMOS實時時鐘(RTC)和日歷���,針對低功耗進行了優(yōu)化���。還提供了可編程時鐘輸出、中斷輸出和低電壓檢測器�。所有地址和數(shù)據(jù)通過雙線雙向I2C總線串行傳輸。最大總線速度為

2023-04-03 14:10:43

PCA9544A是NXP公司生產(chǎn)的I2C總線多路復(fù)用器�����,通過該器件可以將一路I2C總線擴展為4路I2C總線�。將1路上行SDA/SCL通道擴展為4路下行通道。通過對內(nèi)部可編程寄存器進行配置�,在同一

2010-03-12 14:49:43 59

59 PCA9546A 是一款I(lǐng)2C 多路復(fù)用器和開關(guān),能實現(xiàn)I2C 總線擴展�����、電平轉(zhuǎn)換及總線功能恢復(fù)

2010-03-12 15:14:43 74

74 I2C 總線實驗(實時時鐘��、EEPROM 和ZLG7290 的實驗)

一. 實驗?zāi)康募由钣脩魧2C 總線的理解��,熟悉I2C 器件的使用

2008-09-22 16:58:40 4026

4026

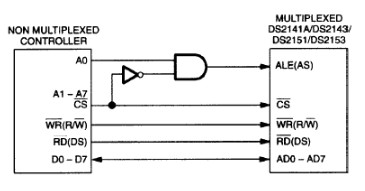

基于CPLD的非多路復(fù)用與多路復(fù)用總線轉(zhuǎn)換橋的設(shè)計與實現(xiàn)

微處理器對外并行總線接口方式一般分為兩種����,一種為多路復(fù)用方式,數(shù)據(jù)與地址采用共用引腳���,分時傳輸�����;另一

2009-03-28 15:08:27 753

753

非多路復(fù)用與多路復(fù)用總線轉(zhuǎn)換橋的設(shè)計與實現(xiàn)

提出了一種新穎的非多路復(fù)用總線與多路復(fù)用總線的轉(zhuǎn)換接口電路���。以兩種總線的典型代表芯片TMS

2009-03-28 15:14:29 798

798

摘要:提出了一種新穎的非多路復(fù)用總線與多路復(fù)用總線的轉(zhuǎn)換接口電路�����。以兩種總線的典型代表芯片TMS320F206與SJA1000為例���,分

2009-06-20 13:20:32 659

659

復(fù)用器的多路復(fù)用

多路復(fù)用是

2010-01-07 14:27:22 1117

1117 頻分多路復(fù)用(FDM),頻分多路復(fù)用(FDM)是什么意思

“復(fù)用”是一種將若干個彼此獨立的信號���,合并為一個可在同一信道上同時傳輸?shù)膹?fù)合信號的方法���。

2010-03-19 14:00:58 7211

7211 時分多路復(fù)用(TDM),時分多路復(fù)用(TDM)的原理是什么?

為了提高信道利用率,使多個信號沿同一信道傳輸而互相不干擾��,稱

2010-03-19 14:07:02 9163

9163 時分多路復(fù)用(TDM),時分多路復(fù)用(TDM)是什么意思

這種方法是把傳輸信道按時間來分割�,為每個用戶指定一個時間間隔,每個間隔里傳輸信號

2010-04-03 15:28:18 5419

5419 1. 概述MM58167B作為總線型微處理系統(tǒng)中的實時時鐘源�����,其內(nèi)部包括一個可尋址的實時計數(shù)器�、56 bit片內(nèi)RAM和

2010-11-11 17:12:06 801

801

1553B總線是MIL-STD-1553總線的簡稱�����,其中B就是BUS���,MIL-STD-1553B總線是飛機內(nèi)部時分制命令/響應(yīng)式多路復(fù)用數(shù)據(jù)總線���。

2011-04-19 13:42:53 2740

2740 DS1339A串行實時時鐘(RTC)是低功耗的時鐘/日歷芯片,具有兩個可編程日歷鬧鐘與一路可編程方波輸出。地址與數(shù)據(jù)通過I2C總線串行傳送���。時鐘/日歷可提供秒��、分�、時�、星期、日期�����、月���、

2013-04-23 09:52:03 70

70 數(shù)據(jù)總線DB用于傳送數(shù)據(jù)信息����。地址總線AB是專門用來傳送地址的,由于地址只能從CPU傳向外部存儲器或I/O端口�,所以地址總線總是單向三態(tài)的,這與數(shù)據(jù)總線不同�����。

2017-11-13 09:09:39 33371

33371

總線可分成CPU總線�����,存儲器總線����,I/O通道總線和外圍接口總線四個層次。每個層次的總線又分為地址總線����、控制總線、數(shù)據(jù)總線等三種��。地址總線和控制總線上的信號是由執(zhí)行總線操作的主設(shè)備產(chǎn)生的,CPU

2017-11-16 14:56:56 59442

59442 作者:薩其日娜 內(nèi)蒙古魯電電力工程有限公司 摘要: 應(yīng)用MicroBlaze軟核作為CPU的硬件平臺�����,在此平臺上設(shè)計了基于AXI總線的通用實時時鐘IP核����。給出了創(chuàng)建IP核的過程和導入IP核的方法

2017-11-17 16:34:42 3694

3694 AiP8563是低功耗的CMOS實時時鐘/日歷芯片���,它提供一個可編程時鐘輸出,一個中斷輸出和掉電檢測器���,所有的地址和數(shù)據(jù)通過rc總線接口串行傳遞。最大總線速度為400Kbits/s��,每次讀寫數(shù)據(jù)后���,內(nèi)嵌的字地址寄存器會自動產(chǎn)生增量��。廣泛應(yīng)用于移動電話��、便攜儀器、傳真機�����、電池電源產(chǎn)品���。

2019-02-27 08:00:00 22

22 HYM8563 是一款低功耗CMOS實時時鐘/日歷芯片�����,它提供一個可編程的時鐘輸出���,一個中斷輸出和一個掉電檢測器���,所有的地址和數(shù)據(jù)都通過I2C總線接口串行傳遞��。最大總線速度為 400Kbits/s�,每次讀寫數(shù)據(jù)后��,內(nèi)嵌的字地址寄存器會自動遞增。

2019-03-28 08:00:00 37

37 電子發(fā)燒友網(wǎng)站提供《AD9559/PCBZ 時鐘多路復(fù)用器參考設(shè)計.pdf》資料免費下載

2020-12-31 06:31:59 11

11 電子發(fā)燒友網(wǎng)站提供《AD9558/PCBZ 時鐘多路復(fù)用器參考設(shè)計.pdf》資料免費下載

2020-12-31 06:34:39 14

14 電子發(fā)燒友網(wǎng)站提供《AD9552/PCBZ 時鐘多路復(fù)用器參考設(shè)計.pdf》資料免費下載

2020-12-31 06:37:03 19

19 電子發(fā)燒友網(wǎng)站提供《AD9557/PCBZ 時鐘多路復(fù)用器參考設(shè)計.pdf》資料免費下載

2020-12-31 06:40:42 9

9 1553B總線是MIL-STD-1553總線的簡稱����,其中B就是BUS,MIL-STD-1553B總線是飛機內(nèi)部時分制命令/響應(yīng)式多路復(fù)用數(shù)據(jù)總線��。

2021-01-25 10:20:06 6862

6862 LTC4312:帶總線緩沖器的引腳可選2通道2線多路復(fù)用器數(shù)據(jù)表

2021-04-15 19:32:00 5

5 LTC1391:帶級聯(lián)串行接口的8通道模擬多路復(fù)用器數(shù)據(jù)表

2021-04-28 19:49:10 9

9 ADG3249:2.5 V/3.3 V�����,2:1多路復(fù)用器/多路分解器總線開關(guān)數(shù)據(jù)表

2021-04-29 11:30:26 4

4 ADG3248:2.5 V/3.3 V��,2:1多路復(fù)用器/多路分解器總線開關(guān)數(shù)據(jù)表

2021-04-29 12:40:52 10

10 LTC4314:引腳可選4通道2線多路復(fù)用器�,帶總線緩沖器數(shù)據(jù)表

2021-05-07 16:23:04 8

8 LTC4305:帶電容緩沖的2通道、2線總線多路復(fù)用器數(shù)據(jù)表

2021-05-08 19:31:47 8

8 LTC4306:帶電容緩沖的4通道2線總線多路復(fù)用器數(shù)據(jù)表

2021-05-08 20:53:39 8

8 LTC1390:帶串行接口的8通道模擬多路復(fù)用器數(shù)據(jù)表

2021-05-21 11:26:26 1

1 實時時鐘的縮寫是RTC(Real_Time Clock)實時時鐘是一個獨立的定時器����。RTC模塊擁有一組連續(xù)計數(shù)的計數(shù)器,在相應(yīng)軟件配置下����,可提供時鐘日歷的功能。修改計數(shù)器的值可以重新設(shè)置系統(tǒng)當前

2021-12-02 16:51:18 5

5 AiP8563是低功耗的CMOS實時時鐘/日歷芯片����,它提供一個可編程時鐘輸出�,一個中斷輸出和掉電檢測器�,所有的地址和數(shù)據(jù)通過IC總線接口串行傳遞。最大總線速度為400Kbits/s�,每次讀寫數(shù)據(jù)后,內(nèi)嵌的字地址寄存器會自動產(chǎn)生增量����。廣泛應(yīng)用于移動電話、便攜儀器���、傳真機���、電池電源產(chǎn)品。

2022-10-10 10:47:21 1

1 AiP8563可以替代 HYMATNXP�����,TSC 已量產(chǎn)可節(jié)省BOM成本

是低功耗的 CMOS 實時時鐘/日歷芯片��,它提供一個可編程時鐘輸出����,一個中斷輸出和掉電檢測器��,所有的地址和數(shù)據(jù)

2022-10-27 16:19:11 3

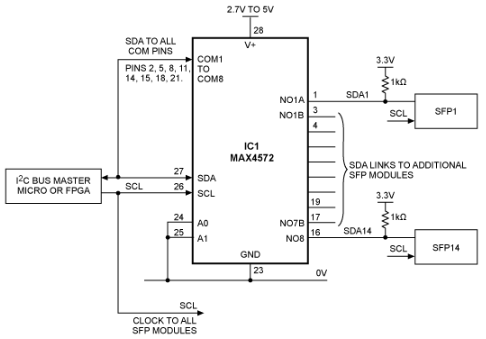

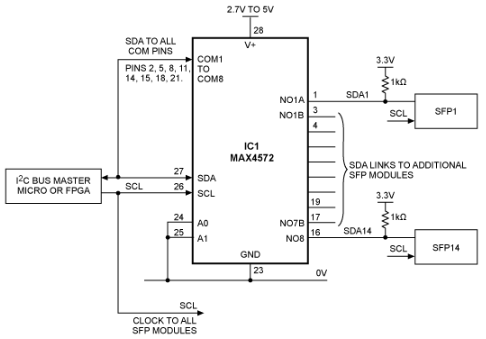

3 為避免在帶有SFP模塊的電信或數(shù)據(jù)通信系統(tǒng)中出現(xiàn)多個I2C總線主站,請?zhí)砑幽M多路復(fù)用器(MAX4572)��,將數(shù)據(jù)線引導至相應(yīng)的SFP模塊��。

2023-02-08 16:36:45 778

778

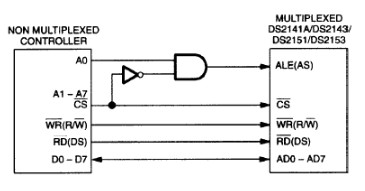

本應(yīng)用筆記包含將非多路復(fù)用總線處理器連接至以下達拉斯半導體T1或E1成幀器和單芯片收發(fā)器(SCT)所需的信息:DS2141A���、DS2143��、DS2151或DS2153�。這些器件最初設(shè)計用于與使用多路復(fù)用總線配置的處理器接口�。

2023-02-09 12:08:21 540

540

I2C總線接口的實時時鐘/日歷芯片封裝:SOP8_150MIL

2022-08-19 16:00:10 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評論