聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

EPSON

+關(guān)注

關(guān)注

1文章

145瀏覽量

87770 -

鎖相環(huán)電路

+關(guān)注

關(guān)注

0文章

15瀏覽量

12243 -

高頻輸出

+關(guān)注

關(guān)注

0文章

6瀏覽量

1031

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

?CDCVF2510 3.3V鎖相環(huán)時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

該CDCVF2510是一款高性能、低偏斜、低抖動(dòng)、鎖相環(huán) (PLL) 時(shí)鐘驅(qū)動(dòng)器。它使用鎖相環(huán) (PLL) 將反饋 (FBOUT) 輸出與時(shí)鐘 (CLK) 輸入信號(hào)在頻率和相位上精確對(duì)

?CDCVF25081 3.3-V 鎖相環(huán)時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

CDCVF25081是一款高性能、低偏斜、低抖動(dòng)、鎖相環(huán)時(shí)鐘驅(qū)動(dòng)器。它使用 PLL 將輸出時(shí)鐘在頻率和相位上精確對(duì)齊輸入時(shí)鐘信號(hào)。輸出分為 2 個(gè)組,總共 8 個(gè)緩沖 CLKIN

?CDCVF2510A 3.3V鎖相環(huán)時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

該CDCVF2510A是一款高性能、低偏斜、低抖動(dòng)、鎖相環(huán) (PLL) 時(shí)鐘驅(qū)動(dòng)器。該CDCVF2510A使用鎖相環(huán) (PLL) 將反饋 (FBOUT) 輸出在頻率和相位上精確對(duì)齊到時(shí)

基于鎖相環(huán)的無軸承同步磁阻電機(jī)無速度傳感器檢測(cè)技術(shù)

使用場(chǎng)合。為實(shí)現(xiàn)無軸承同步磁阻電機(jī)高速超高速、低成本、實(shí)用化運(yùn)行,提出了一種基于鎖相環(huán)法的無速度傳感自檢測(cè)技術(shù)。通過應(yīng)用鎖相環(huán)原理,設(shè)計(jì)出無軸承同步磁阻電機(jī)無速度傳感器,并基于 Matlab

發(fā)表于 07-29 16:22

高壓放大器在鎖相環(huán)穩(wěn)定重復(fù)頻率研究中的應(yīng)用

頻率的鎖相環(huán)理論和關(guān)鍵器件,以及結(jié)果分析。 測(cè)試設(shè)備: 高壓放大器、光電探測(cè)器、低通濾波器、比例積分控制器、PZT等。 圖1:穩(wěn)定重復(fù)頻率的鎖相環(huán)系統(tǒng)結(jié)構(gòu)圖 實(shí)驗(yàn)過程: 系統(tǒng)結(jié)構(gòu)圖如圖1所示,從NPR鎖模光纖激光器耦合出一部分光

鎖相環(huán)(PLL)電路設(shè)計(jì)與應(yīng)用(全9章)

內(nèi)容介紹本文檔主要介紹鎖相環(huán)(PLL)電路的設(shè)計(jì)與應(yīng)用,內(nèi)容包括PLL工作原理與電路構(gòu)成、PLL電路的傳輸特性、PLL電路中環(huán)路濾波器的設(shè)計(jì)

發(fā)表于 04-18 15:34

基于運(yùn)算放大器和模擬集成電路的電路設(shè)計(jì)(第3版)

內(nèi)容介紹:

本文全面闡述以運(yùn)算放大器和模擬集成電路為主要器件構(gòu)成的電路原理、設(shè)計(jì)方法和實(shí)際應(yīng)用。電路設(shè)計(jì)以實(shí)際器件為背景,對(duì)實(shí)現(xiàn)中的許多實(shí)際問題尤為關(guān)注。全書共分13章,包含三大部分。

發(fā)表于 04-16 14:34

愛普生(EPSON) 集成電路IC

隨著技術(shù)的發(fā)展,Epson在集成電路(IC)方面的研發(fā)和生產(chǎn)也逐步成為其重要的業(yè)務(wù)之一。Epson的集成電路主要應(yīng)用于各種電子設(shè)備中,包括消

鎖相環(huán)是什么意思

鎖相環(huán)(Phase-Locked Loop,簡(jiǎn)稱PLL)是一種廣泛應(yīng)用于電子系統(tǒng)中的反饋控制系統(tǒng),主要用于頻率合成和相位同步。本文將從鎖相環(huán)的工作原理、基本組成、應(yīng)用案例以及設(shè)計(jì)考慮等方面進(jìn)行詳細(xì)闡述,以幫助讀者全面理解這

AN-1420:利用數(shù)字鎖相環(huán)(DPLL)實(shí)現(xiàn)相位增建和無中斷切換

電子發(fā)燒友網(wǎng)站提供《AN-1420:利用數(shù)字鎖相環(huán)(DPLL)實(shí)現(xiàn)相位增建和無中斷切換.pdf》資料免費(fèi)下載

發(fā)表于 01-13 14:07

?0次下載

可編程晶振的鎖相環(huán)原理

鎖相環(huán)(Phase-LockedLoop,PLL)是一個(gè)能夠比較輸出與輸)入相位差的反饋系統(tǒng),利用外部輸入的參考信號(hào)控制環(huán)路內(nèi)部振蕩信號(hào)的頻率和相位,使振蕩信號(hào)同步至參考信號(hào)。而鎖相環(huán)

基于鎖相環(huán)法的載波提取方案

電子發(fā)燒友網(wǎng)站提供《基于鎖相環(huán)法的載波提取方案.pdf》資料免費(fèi)下載

發(fā)表于 01-07 14:41

?2次下載

TMS320C6000 DSP軟件可編程鎖相環(huán)控制器指南

電子發(fā)燒友網(wǎng)站提供《TMS320C6000 DSP軟件可編程鎖相環(huán)控制器指南.pdf》資料免費(fèi)下載

發(fā)表于 12-24 16:54

?0次下載

基于滑模觀測(cè)器和鎖相環(huán)的無軸承感應(yīng)電機(jī)無速度傳感器控制

電子發(fā)燒友網(wǎng)站提供《基于滑模觀測(cè)器和鎖相環(huán)的無軸承感應(yīng)電機(jī)無速度傳感器控制.pdf》資料免費(fèi)下載

發(fā)表于 12-19 14:04

?0次下載

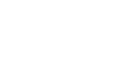

EPSON(愛普生)獲得高頻輸出的方法(第一部:鎖相環(huán)電路)

EPSON(愛普生)獲得高頻輸出的方法(第一部:鎖相環(huán)電路)

評(píng)論