聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

Xilinx

+關(guān)注

關(guān)注

73文章

2192瀏覽量

129806 -

Vivado

+關(guān)注

關(guān)注

19文章

846瀏覽量

70430

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

vivado時序分析相關(guān)經(jīng)驗

vivado綜合后時序為例主要是有兩種原因?qū)е拢?1,太多的邏輯級

2,太高的扇出

分析時序違例的具體位置以及原因可以使用一些tcl命令方便快速得到路徑信息

發(fā)表于 10-30 06:58

vcs和vivado聯(lián)合仿真

我們在做參賽課題的過程中發(fā)現(xiàn),上FPGA開發(fā)板跑系統(tǒng)時,有時需要添加vivado的ip核。但是vivado仿真比較慢,vcs也不能直接對添加了vivado ip核的soc系統(tǒng)進行仿真。在這種情況下

發(fā)表于 10-24 07:28

Vivado中向FPGA的Flash燒錄e203的方法

首先導(dǎo)入、并配置好項目,完成項目的綜合(SYNTHESIS)與實現(xiàn)(IMPLEMENTATION),查看有無錯誤與或警告信息,調(diào)整完成后,右鍵比特流生成(Generate Bitstream),選擇

發(fā)表于 10-23 08:28

vivado仿真時GSR信號的影響

利用vivado進行設(shè)計xilinx FPGA時,寫完設(shè)計代碼和仿真代碼后,點擊run simulation(啟動modelsim進行仿真)。

Vivado無法選中開發(fā)板的常見原因及解決方法

在使用 AMD Vivado Design Suite 對開發(fā)板(Evaluation Board)進行 FPGA 開發(fā)時,我們通常希望在創(chuàng)建工程時直接選擇開發(fā)板,這樣 Vivado 能夠自動配置

如何使用One Spin檢查AMD Vivado Design Suite Synth的結(jié)果

本文講述了如何使用 One Spin 檢查 AMD Vivado Design Suite Synth 的結(jié)果(以 Vivado 2024.2 為例)。

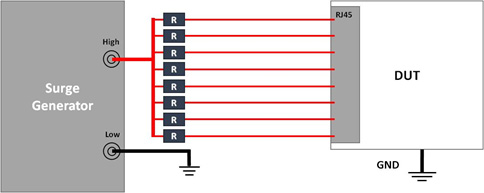

“System Level EOS Testing Method”可以翻譯為: “系統(tǒng)級電性過應(yīng)力測試方法”

“System Level EOS Testing Method”可以翻譯為:

“系統(tǒng)級電性過應(yīng)力測試方法”

Vivado 2018.3軟件的使用教程

大家好,歡迎來到至芯科技FPGA煉獄營地,準(zhǔn)備開啟我們的偉大征程!正所謂“兵馬未動,糧草先行”,戰(zhàn)前的準(zhǔn)備自是必不可少,在FPGA的漫漫沙場,我們何以入場,何以取勝呢?在這里我們?yōu)楦魑粦?zhàn)友準(zhǔn)備了vivado 2018.3的使用教程。

Vivado FIR IP核實現(xiàn)

Xilinx的FIR IP核屬于收費IP,但是不需要像 Quartus那樣通過修改license文件來破解。如果是個人學(xué)習(xí),現(xiàn)在網(wǎng)絡(luò)上流傳的license破解文件在破解Vivado的同時也破解

Vivado Design Suite用戶指南: 設(shè)計分析與收斂技巧

電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite用戶指南: 設(shè)計分析與收斂技巧.pdf》資料免費下載

發(fā)表于 01-15 15:28

?2次下載

Vivado Design Suite用戶指南:邏輯仿真

電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite用戶指南:邏輯仿真.pdf》資料免費下載

發(fā)表于 01-15 15:25

?0次下載

使用HLS流程設(shè)計和驗證圖像信號處理設(shè)備

STMicroelectronics成像部門負(fù)責(zé)向消費者、工業(yè)、安全和汽車市場提供創(chuàng)新的成像技術(shù)和產(chǎn)品。該團隊精心制定了一套通過模板實現(xiàn)的High-Level Synthesis(HLS)高層次綜合流程,使得上述產(chǎn)品能夠迅速上市。對于汽車市場,該流程符合ISO 26262

從Level1 Model到Level3 Modle來感受器件模型是如何開發(fā)的

? ? ? ?本文從Level1 model到Level3 model的Ids電流公式的發(fā)展來感受Compact器件模型是如何開發(fā)的。 MOS技術(shù)擴展到納米尺寸,帶來了電路模擬器中器件模型的發(fā)展

求助,ISO7721用于485隔離遇到的疑問求解

我想選用ISO7721用于485隔離,遇到帶你問題,請幫忙看看。

①看到PDF上描述IIH(High-level input current)最大到10uA,但是MCU SCI TX引腳輸出一般

發(fā)表于 12-18 06:30

Getting Started with Vivado High-Level Synthesis

Getting Started with Vivado High-Level Synthesis

評論