6改變DS5暗著改變、DS5改變DS4暗著改變����、DS4改變DS3暗著改變�����、DS3改變DS2暗著改變、DS2改變DS1暗著改變�����、DS1改變DS6暗著改變后一位暗亮是DS1改變DS2暗著改變����、DS2改變DS3

2013-05-27 20:18:02

XRT7300是DS3 / E3 / STS-1收發(fā)器(線路接口單元)的組合,設(shè)計(jì)用于多標(biāo)準(zhǔn)網(wǎng)絡(luò)和傳輸系統(tǒng)

2019-09-03 08:40:00

是數(shù)組的錯(cuò)誤�,但我找不到有什么錯(cuò)誤,程序如下:#include "ds1302.h"#include #includeunsigned char time_buf1[8

2012-12-28 11:24:32

DS3141 SINGLE DS3/E3 FRAMER

2023-04-06 11:50:41

IC FRAMER TRPL DS3/E3 144TCBGA

2023-04-06 11:50:41

IC FRAMER QUAD DS3/E3 144TCBGA

2023-04-06 11:50:40

IC FRAMER 6PORT DS3/E3 HCBGA

2023-03-23 05:00:06

IC FRAMER 6PORT DS3/E3 HCBGA

2023-03-23 05:00:06

IC LIU DS3/E3/STS-1 28-PLCC

2023-04-06 11:48:58

IC TXRX DS3/E3 CSBGA

2023-04-06 16:10:19

IC TXRX DS3/E3 CSBGA

2023-04-06 17:07:15

IC LIU DS3/E3/STS-1 144CBSGA

2023-04-06 11:50:44

IC LIU DS3/E3/STS-1 144CBSGA

2023-04-06 11:50:42

Testing Embedded SoftwareForeword xPreface xiiiAcknowledgments xviPart I Introduction xix1

2008-09-19 09:42:46

error rate calculation 和display 模塊 如何連接 急求!����! error rate calculation 的輸出端子怎么出來,還有一個(gè) scope 的輸入端子 怎么增加一個(gè) , 急求�!萬分感謝

2012-05-10 14:34:24

ADS1278 MODE SELECTION和DATA RATE的選擇對GAIN ERROR是否有影響���?datasheet中的GAIN ERROR是在哪個(gè)采樣率下測得的結(jié)果�����?

2024-11-22 06:51:09

CYUSB3304 DS3的2.0和3.0連接了不同的設(shè)備����,DS3我們2.0接了一個(gè)F9P�����,3.0接了一個(gè)5G模組,請問這樣是否會(huì)有問題�����?謝謝

2024-02-28 08:14:18

我在esp32-C3的esp now demo里切換了速率,在

esp_wifi_start后添加了

esp_wifi_config_espnow_rate(ESPNOW_WIFI_IF

2024-06-27 08:31:08

GSM / EDGE Base Station Bit Error Rate Testing with CMU300This Application Note provides

2009-09-24 09:08:59

in the design.ERROR:PhysDesignRules:10 - The networkis completely unrouted.生成bit文件時(shí)報(bào)錯(cuò)���,也沒有tx_clk_OBUF這個(gè)信號

2016-11-29 20:39:35

、accel�、ds3 and ds4 no decimation

fifo odr: 104Hz

fifo threshold level: 24 * 80

fifo mode: Continuous mode (110)

2024-03-27 06:05:07

, bit error rate testing, DC power interface, data storage and standard RS422 and IEEE 1553 signal interfaces for satellite panel and unit testing.

2018-10-16 13:11:52

;***it DS2=P3^5;***it DS3=P3^6; ***it ledlk=P1^0; ***it smglk=P1^1;***it smgbitlk=P1^2

2013-04-27 23:02:29

2g_rate -h 15 -b 40

wl: 錯(cuò)誤 -29

root@:~/BM28_Test_Script/wifi/tx#wl 5g_rate -h 15 -b 40

wl: error -29

2024-06-03 07:27:48

���? #output-data-rate#lsm6ds3 #power-consumption以上來自于谷歌翻譯以下為原文 Hello.I am curious about the power consumption of the LSM6DS3

2018-09-10 17:18:54

;***it DS2=P3^5;***it DS3=P3^6; ***it ledlk=P1^0; ***it smglk=P1^1;***it smgbitlk=P1^2

2013-04-27 23:04:43

Traditionally, bit error rate testing compares the bits from a Device Under Test (DUT) against a

2019-09-24 09:22:33

DS3170DK 是一款專為評估DS3170 DS3/E3 單芯片收發(fā)器(SCT)而設(shè)計(jì)的集成開發(fā)板����。該開發(fā)板包括評估DS3170 各種工作模式所需的全部電路�����,開發(fā)板還帶有微處理器����,可以實(shí)時(shí)運(yùn)行代

2008-04-15 12:53:15 35

35 DS3170DK 是一款專為評估 DS3170 DS3/E3 單芯片收發(fā)器(SCT)而設(shè)計(jì)的集成開發(fā)板。該開發(fā)板包括評估DS3170 各種工作模式所需的全部電路��,開發(fā)板還帶有微處理器,可以實(shí)時(shí)運(yùn)行代

2008-04-15 13:02:46 0

0 Bit Error Rate Testing (BERT)_Chinese.avi

分析儀的比特誤差率測試視頻,中文哦。

2008-09-09 10:24:01 30

30 layer to DS3, E3, andSTS-1 lines. The receiver performs clock and datarecovery, B3ZS/HDB3 decoding, and loss-of-signalmon

2008-09-19 16:18:01 20

20 Dynamic Testing Method for Yarn Tension

Ahshmct Various dynamic test devices of tam tension

2009-01-21 11:58:13 15

15 Testing method of printed wiring board to find out short-circuit failure

2009-03-24 14:04:19 0

0 Implementing Double Data Rate I/O Signaling in Cyclone Devices

Double data rate (DDR) transmission

2009-05-14 10:44:26 24

24 The CAN protocol provides for programming of the bit rate, and the number and location of data

2009-06-18 10:44:41 19

19 temperature andrecords the result in a protected memory section. Therecording is done at a user-defined rate. A total of 81928-bit

2009-06-19 08:19:57 17

17 iButton DESCRIPTIONThe DS1971 256-bit EEPROM iButton is a rugged read/write data carrier

2009-07-30 22:59:18 36

36 Although not recommended,smaller input signals are tolerable. Figure 8, 14, and20 show the bit error rate performance versus input s

2009-09-15 08:21:26 14

14 Heart Rate and EKG Monitor using the MSP430FG439:This application report describes how to build a

2009-09-25 15:49:02 14

14 Slew Rate of Op Amp Circuits:The slew rate (SR) is defined as the maximum rate of change

2009-09-26 10:45:51 12

12 The DS92LV16 Serializer/Deserializer (SERDES) pair transparentlytranslates a 16–bit parallel bus

2009-10-14 09:07:06 33

33 The DS92LV18 Serializer/Deserializer (SERDES) pair transparentlytranslates a 18–bit parallel bus

2009-10-14 09:09:43 24

24 ). It contains a low power, high speed, 14-bit sampling ADC, an internal conversion clock, an internal reference (and buffer), error correction ci

2009-11-21 14:19:01 26

26 Smart FET Robustness Testing

Agenda• Repetitive Clamp Testing• Repetitive Short Circuit Testing̶

2010-04-16 10:53:50 18

18 features Fast Throughput Rate: 1.25 MSPS at 5 V, 625 KSPS at 3 V Wide Analog Input: 0 V

2010-06-06 15:13:59 18

18 1FEATURESAPPLICATIONS2 3R26; Maximum Sample Rate: 65MSPSR26; 10-Bit ResolutionR26; No Missing

2010-06-07 12:30:25 17

17 ; Codes canachieve bit error rate near to Shannon limit. They canbe decoded using soft decision iterative decodingscheme. As lo

2010-07-05 11:08:01 4

4 signal/noise ratio for analog receivers,and reduces bit error rate in digital receivers.As a parameter in a communications l

2010-07-08 15:30:03 11

11 Product Features•Cell based implementation•Selectable mode as DS1 or DS3

2010-07-10 10:14:25 12

12 The Available Bit Rate (ABR) service category is the most complex ATM traffic type yet defined

2010-07-10 11:23:37 7

7 Testing AT

2010-07-10 11:32:20 13

13 This application note presents thefundamental measurement principlesinvolved in testing

2010-07-12 14:17:37 8

8 technology development. Innovations like oscilloscopes, logicanalyzers and bit error ratio testers have enabled new, faster and more

2010-07-14 10:48:36 14

14 UnderTest) on a single functional testsystem. Testing a single UUT functionally is hard enough,and testing more

2010-07-22 14:57:43 6

6 of 89 GPa.1 In the work described here, an Agilent T150 universal testing machine (UTM) was used to meas

2010-08-13 10:11:08 6

6 Trompeter公司推出系列75Ω DS3同軸電纜BNC插頭——SureNotch BNC插頭。該器件在中央局DS3

2006-03-13 13:09:05 926

926 DS3150 業(yè)內(nèi)首款單端口T3/E3 LIU,集成了抖動(dòng)衰減器

DS3150可以實(shí)現(xiàn)在物理層與DS3����、E3和STS-1線路接口的所有必要功能���。接收器可以實(shí)現(xiàn)時(shí)鐘和數(shù)據(jù)恢復(fù)��、

2008-09-19 16:20:07 1682

1682

Multiply Your Sampling Rate with Time-Interleaved Data Converters

Abstract: Interleaving multiple

2009-04-16 15:54:20 1815

1815

Abstract: DS2172 Bit Error Rate Tester (BERT) simplified receiver operation during repetitive

2009-04-18 11:34:44 695

695

Abstract: This application note explains how to configure the bit-error-rate tester (BERT

2009-04-18 11:39:25 1202

1202 摘要:本應(yīng)用筆記介紹不用改動(dòng)外部元件�����,如何來調(diào)整DS3254�����、DS3253�、DS3252和DS3251 DS3�����、E3����、STS-1線路接口單元(LIU)的脈沖設(shè)置,包括幅度和脈沖波形等�����。 DS3254�、D

2009-04-18 11:47:53 864

864 Abstract: The DS3112 DS3/E3 Multiplex-Framer has three multiplexed modes of operation.

2009-04-18 11:56:08 878

878

摘要:DS3144在一塊硅片上集成了四個(gè)獨(dú)立的DS3/E3成幀器,包括在四路單獨(dú)的DS3或E3信道產(chǎn)生幀并對其進(jìn)行格式化所必需的全部電路��。器件中的每一個(gè)成幀器都是獨(dú)立配置�����,支持具有告

2009-04-20 08:56:19 1897

1897

) controller found in the Dallas Semiconductor DS2155 T1/E1/J1 single chip transceiver (SCT). Testing the bit error rate of a line which carries voic

2009-04-20 09:35:55 957

957 : transmit DS3, DS2, DS1, E3, E2, and E1 clocks and receive DS3, DS2, DS1, E3, E2, and E1 clocks. Since the clocks at the same stage in the circuit

2009-04-20 09:51:19 877

877

Abstract: This application note describes how to reduce current consumption when using the DS

2009-04-21 10:49:55 1304

1304 to communicate with the three digital pots, the DS1267, DS1867, and DS1868, which use this shift register interface for programming. The DS3

2009-04-28 11:50:56 998

998

to communicate with the three digital pots, the DS1267, DS1867, and DS1868, which use this shift register interface for programming. The DS3

2009-05-08 09:09:22 865

865

Deluxe Charge Rate Limiter for Small Capacity NiCad Batteries

Here is a deluxe version

2010-01-09 08:23:23 1094

1094

什么是BRI (Basic Rate Interface)

英文縮寫: BRI (Basic Rate Interface)

中文譯名: 基本速率接口

分 類: 電信設(shè)備

2010-02-22 11:14:30 1956

1956 DS3170集成了DS3/E3成幀器和LIU (單芯片收發(fā)器)���,與DS3/E3物理層銅纜接口

2011-04-01 11:09:43 2471

2471

IC with a DDR3 memory chip. The DS34S132 uses an external double data rate (DDR) synchronous DRAM (or DDR1) device to buffer data. The memor

2011-08-29 10:20:00 41

41 (RTCs), including the DS3231,DS3232, DS3234, DS32B35, and DS32C35, to help customers identify the proper solution for their application. The DS3

2011-09-27 11:27:08 28

28 在使用電腦中有時(shí)候會(huì)遇到unknown hard error,很多人不知道unknown hard error什么意思�����。電腦出現(xiàn)hard error是因?yàn)槭裁?����,unknown hard error解決方法什么�����,在本內(nèi)容中都一一為大家詳解

2011-12-13 11:23:28 0

0 Error Correcting For 7bit Hamming Code.多種集合�����,符合熱愛PCB繪圖的學(xué)習(xí)者的胃口���,喜歡的朋友下載來學(xué)習(xí)�。

2016-03-21 15:26:25 0

0 Predicting Op Amp Slew Rate Limited Response

2017-03-24 15:16:16 0

0 error rate)或者PER (packet error rate)會(huì)用來考察靈敏度����,在LTE時(shí)代干脆用吞吐量Throughput來定義.

2017-12-11 11:59:58 66860

66860 acceptance testing as a complement to current high dose rate acceptance testing.

2018-06-23 10:40:00 3542

3542 的法國人更是把浪漫與激情大膽地傾注在造車?yán)砟钪?����,打造出個(gè)性非凡的DS3。當(dāng)充滿個(gè)性的DS3來到這個(gè)個(gè)性之風(fēng)愈發(fā)猛烈的國土�,這對我們眼球的刺激無異于27年前崔健首次在工體唱響《一無所有》帶來的震撼。

2018-07-17 11:50:00 5924

5924 現(xiàn)在標(biāo)志汽車正在通過其新的DS3 Dark Side版本的3D打印汽車內(nèi)飾計(jì)劃����,從而加入了寶馬汽車邁向通過3D打印實(shí)現(xiàn)大規(guī)模定制的陣營�。

2018-08-13 09:22:00 1530

1530 本文檔的主要內(nèi)容詳細(xì)介紹的是DS3和DS3E及DS3L系列伺服驅(qū)動(dòng)器的用戶手冊資料免費(fèi)下載。

2018-12-14 10:16:18 11

11 RATE3是一家總部位于新加坡的區(qū)塊鏈公司,由經(jīng)緯中國�、分布式資本�、節(jié)點(diǎn)資本�����、Ledger Capital、Kenetic等國內(nèi)外知名機(jī)構(gòu)投資。項(xiàng)目基于Stellar和Ethereum網(wǎng)絡(luò)開發(fā)跨鏈

2019-01-08 10:47:49 7310

7310 RTD Configurator and Error Budget Calculator

2021-01-27 18:36:18 18

18 出現(xiàn)Error: Unable to reset MCU!的解決方法

2021-10-25 21:06:08 14

14 STM32燒錄 Error:Flash Download Failed-"Cortex-M3" 解決方案—ST-li

2021-12-01 12:06:03 13

13 ba<x>seline_testing.zip

2022-05-05 10:47:17 0

0 3182��、DS3183和DS3184)將ATM小區(qū)/HDLC數(shù)據(jù)包處理器與DS3/E3成幀器和LIU集成在一起���,將ATM小區(qū)或數(shù)據(jù)包映射/解映射為最多四條DS3/E3物理銅線����,每個(gè)端口具有DS3成幀(C位或M23)�����、E3成幀(G.751或G.832)或清通道數(shù)據(jù)流�。

2023-01-12 09:20:13 1602

1602

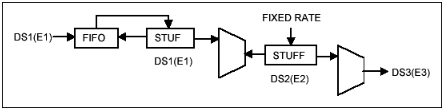

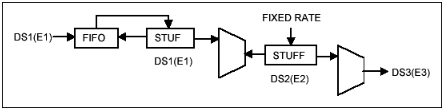

第一級��,即M23級�����,將DS3信號解復(fù)用為7個(gè)獨(dú)立的DS2信號����。不是恢復(fù)單個(gè)DS2時(shí)鐘����,而是創(chuàng)建DS2使能���。七個(gè)DS2使能中的每一個(gè)都處于活動(dòng)狀態(tài)���,每個(gè)DS3幀的DS3時(shí)鐘周期為84 x 7 +(84或83)?�;謴?fù)最后的84或83個(gè)DS3時(shí)鐘周期的決定基于DS2填充位控制。

2023-01-13 10:50:26 2145

2145

DS3112 DS3/E3多路復(fù)用成幀器具有三種多路復(fù)用工作模式。本應(yīng)用筆記描述了器件如何從三種工作模式下的高速多路復(fù)用信號中恢復(fù)低速時(shí)鐘信號。該說明解釋了高速信號中的數(shù)據(jù)如何影響恢復(fù)過程�����。

2023-02-07 11:36:46 1364

1364

本應(yīng)用筆記展示了如何在無映射時(shí)鐘模式下使用ITU O.3模式將增強(qiáng)型誤碼率測試儀(BERT)連接到DS3/E151成幀器。

2023-02-08 11:58:08 1532

1532

DS3144在一塊硅片上集成了四個(gè)獨(dú)立的DS3/E3成幀器,包括在四路單獨(dú)的DS3或E3信道產(chǎn)生幀并對其進(jìn)行格式化所必需的全部電路�����。器件中的每一個(gè)成幀器都是獨(dú)立配置���,支持具有告警檢測與生成功能的M23 DS3、DS3 C位奇偶或G.751幀格式�����。

2023-02-10 11:24:00 1912

1912

在發(fā)射端���,DS3(E3)時(shí)鐘和DS1(E1)時(shí)鐘由輸入引腳派生��,但DS2(E2)時(shí)鐘頻率是DS3(E3)時(shí)鐘頻率的一小部分。出于設(shè)計(jì)原因,分?jǐn)?shù)將表示為整數(shù)比率����,這取決于設(shè)備的模式。DS1(E1)時(shí)鐘可以容忍基于DS3(E3)時(shí)鐘頻率和器件模式的頻率范圍。

2023-02-22 10:10:18 1372

1372

本應(yīng)用筆記介紹如何使用DS3900 PC串口轉(zhuǎn)3線接口與DS1267、DS1867和DS1868三個(gè)數(shù)字電位器通信�,DS3900、DS3223和DS232使用該移位寄存器接口進(jìn)行編程。DS3是一個(gè)

2023-02-25 11:06:19 1961

1961

DS3112具有六種不同的發(fā)送時(shí)鐘和六種不同的接收時(shí)鐘類型:發(fā)送DS3����、DS2�����、DS1����、E3��、E2和E1時(shí)鐘�,以及接收DS3、DS2、DS1�、E3���、E2和E1時(shí)鐘。由于電路中同一級的時(shí)鐘具有相似

2023-06-13 15:39:46 1211

1211

BER���,全稱是,Bit error Rate����,即誤碼率���。

2023-07-03 09:16:08 3086

3086

Audio DS3便攜解碼耳放震撼上市�����,為音頻行業(yè)注入全新技術(shù)活力����! ? ? 關(guān)于 XMOS Powered 重新定義HiFi性能標(biāo)桿 XMOS POWERED 是一套專為高保真(Hi-Fi)音頻市場打造

2025-12-02 10:29:13 536

536

電子發(fā)燒友App

電子發(fā)燒友App

評論