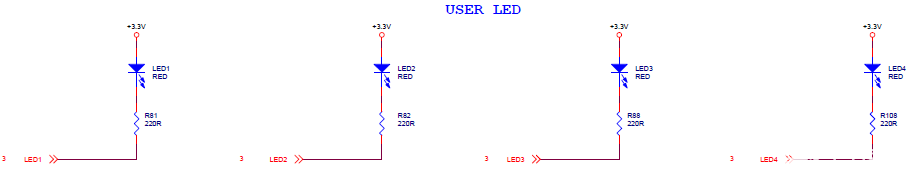

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第二章】LED流水燈實(shí)驗(yàn)及仿真

通過LED流水燈實(shí)驗(yàn),介紹使用PDS軟件開發(fā)FPGA的基本流程,器件選擇、設(shè)置、代碼編寫、編譯、分配....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十章自定義IP實(shí)驗(yàn)

創(chuàng)建自己的IP核有很多好處,例如系統(tǒng)設(shè)計(jì)定制化;設(shè)計(jì)復(fù)用,可以在在IP核中加入license, 有償....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十九章PL端AXI GPIO的使用

使用zynq最大的疑問就是如何把PS和PL結(jié)合起來使用,在其他的SOC芯片中一般都會(huì)有GPIO,本實(shí)....

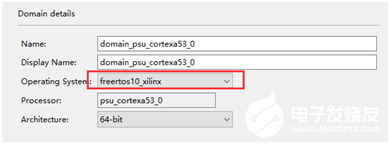

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十一章FreeRTOS實(shí)驗(yàn)

如何搭建Free RTOS實(shí)時(shí)操作系統(tǒng)運(yùn)行環(huán)境,這里不深入探討Free RTOS的具體使用。本實(shí)驗(yàn)以....

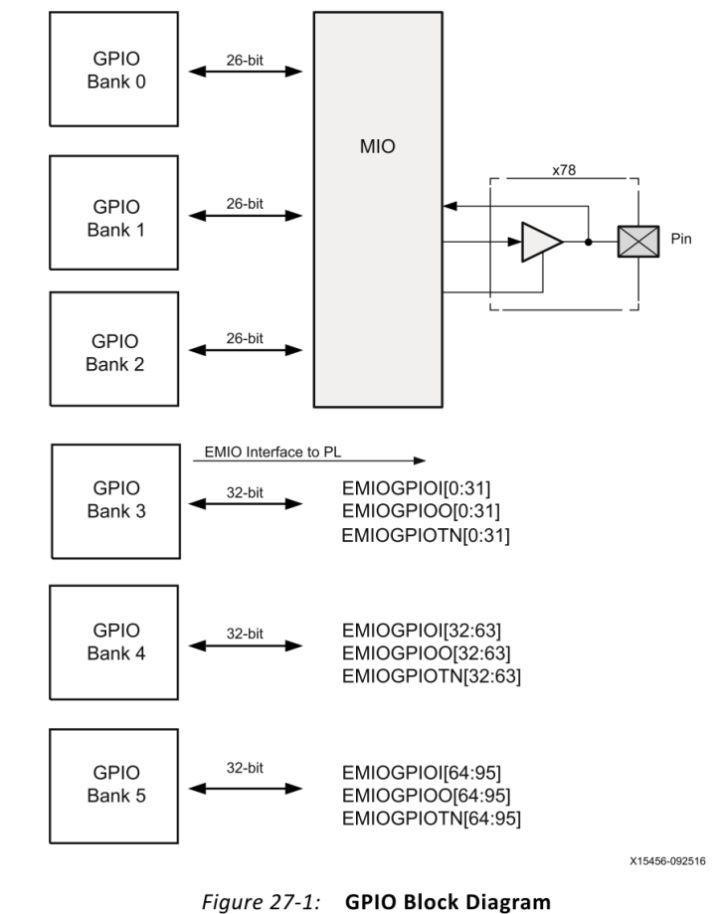

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十八章PS端EMIO的使用

如果想用PS點(diǎn)亮PL的LED燈,該如何做呢?一是可以通過EMIO控制PL端LED燈,二是通過AXI ....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十二章PL讀寫PS端DDR數(shù)據(jù)

PL和PS的高效交互是zynq soc開發(fā)的重中之重,我們常常需要將PL端的大量數(shù)據(jù)實(shí)時(shí)送到PS端處....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十七章System Monitor

本章介紹system monitors的使用,用于監(jiān)測芯片的電壓、溫度值等,也可以通過PL端的ADC....

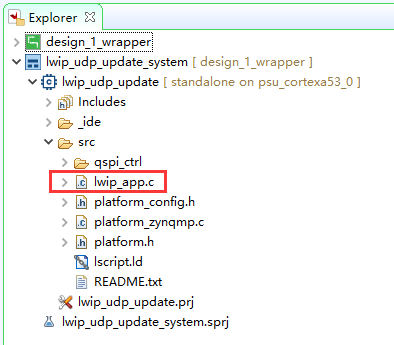

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十六章PS端網(wǎng)絡(luò)遠(yuǎn)程更新QSPI

在實(shí)際工作中,會(huì)遇到產(chǎn)品升級(jí)問題,如果按照程序燒錄的方式,可能需要打開產(chǎn)品的外殼,這無疑。本章介紹一....

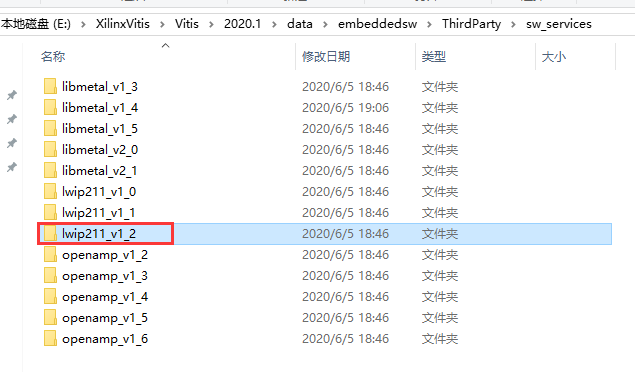

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十五章PS端以太網(wǎng)使用之lwip

開發(fā)板有兩路千兆以太網(wǎng),通過RGMII接口連接,本實(shí)驗(yàn)演示如何使用Vitis自帶的LWIP模板進(jìn)行P....

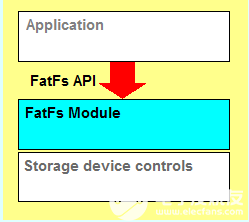

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十四章PS端SD卡讀寫

FatFs是一個(gè)通用的文件系統(tǒng)模塊,用于在小型嵌入式系統(tǒng)中實(shí)現(xiàn)FAT文件系統(tǒng)。FatFs的編寫遵循 ....

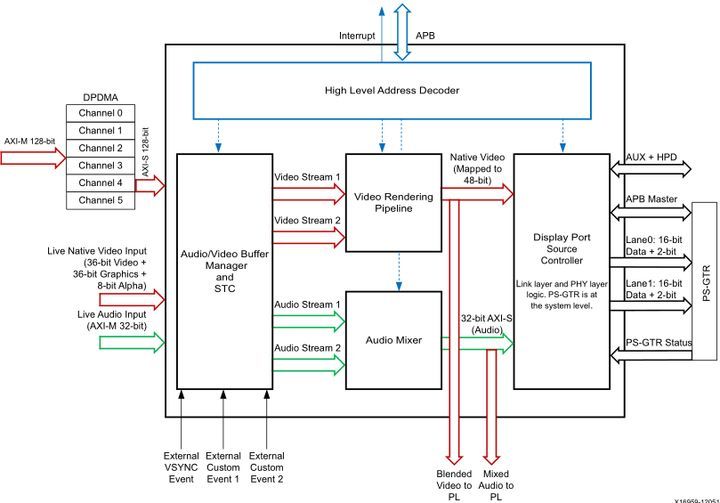

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十三章PS端DP的使用

DisplayPort v1.2協(xié)議,支持4個(gè)5.4G的lane,但本控制器只支持兩個(gè)lane,分辨....

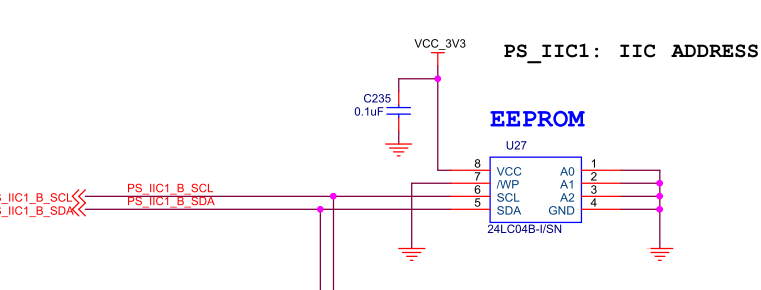

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十二章PS端I2C的使用

ReadBuffer清0,WriteBuffer賦FF寫16個(gè)字節(jié)到EEPROM讀EEPROM的16....

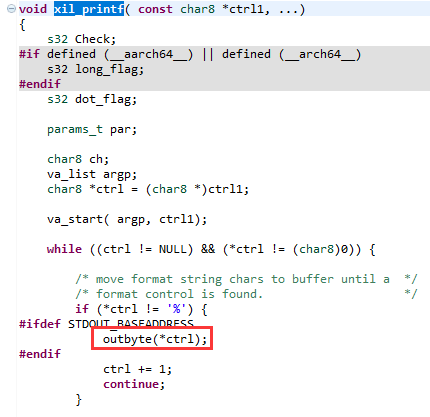

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十一章PS端UART讀寫控制

除了打印信息之外,如果我們想用UART進(jìn)行數(shù)據(jù)傳輸呢?本章便來介紹PS端UART的讀寫控制,實(shí)驗(yàn)中,....

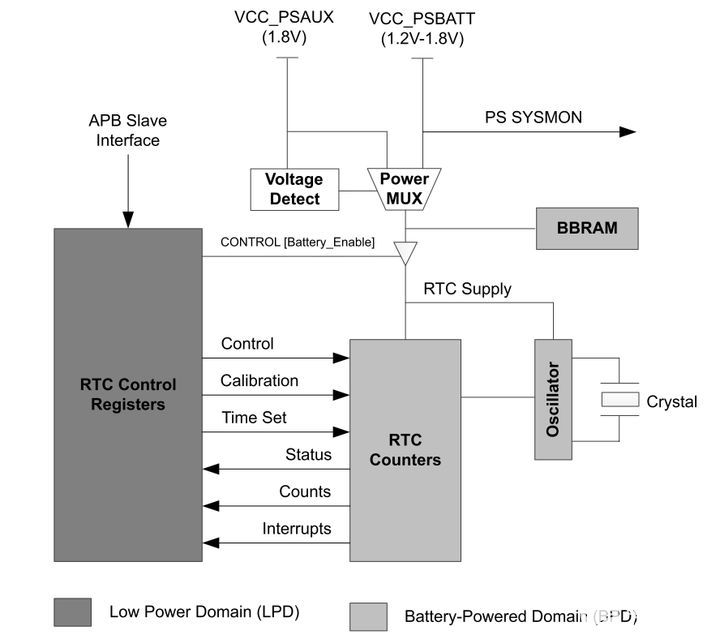

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十章PS端RTC中斷實(shí)驗(yàn)

實(shí)驗(yàn)中通過簡單的修改Vitis的例程,就完成了RTC,中斷的應(yīng)用,看似簡單的操作,但蘊(yùn)含了豐富的知識(shí)....

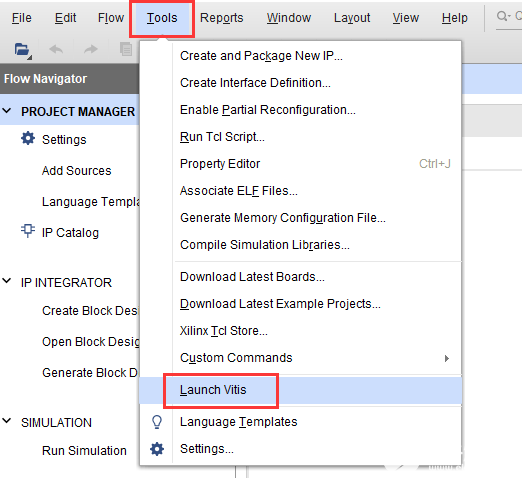

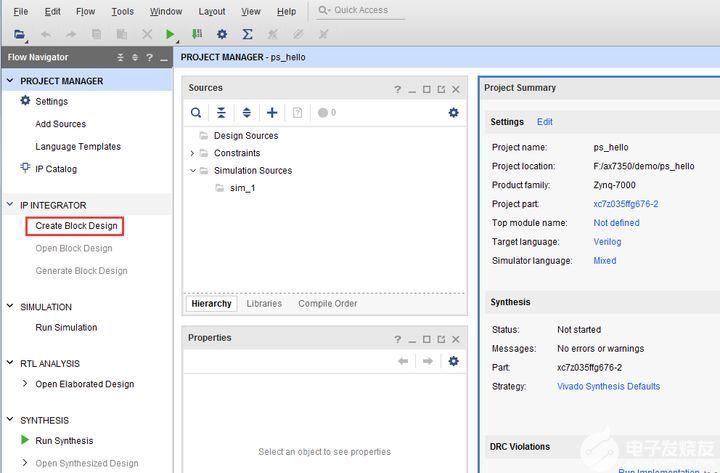

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十九章 Hello World(下)

本章從FPGA工程師和軟件工程師兩者角度出發(fā),介紹了ZYNQ開發(fā)的經(jīng)典流程,F(xiàn)PGA工程師的主要工作....

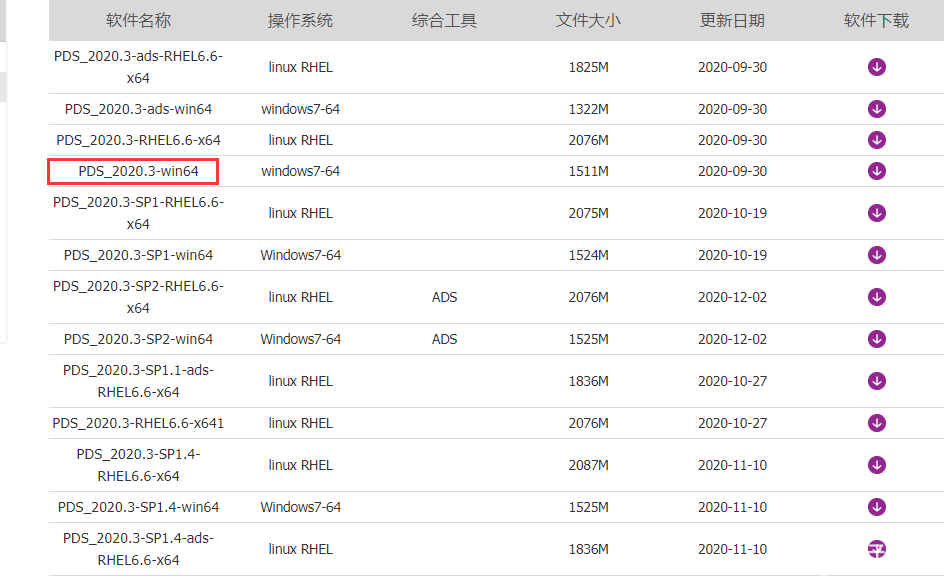

【紫光同創(chuàng)國產(chǎn)FPGA教程 第一章】Pango Design Suite 2020.3安裝

ango Design Suite是深圳市紫光同創(chuàng)電子有限公司的FPGA開發(fā)軟件,截止到目前,軟件的....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十八章 Hello World(上)

我們從原理圖中可以看到ZYNQ芯片分為PL和PS,PS端的IO分配相對(duì)是固定的,不能任意分配,而且不....

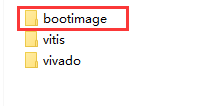

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十七章Vitis準(zhǔn)備工程及注意事項(xiàng)

所有的工程目錄下都有個(gè)bootimage文件夾,存放了對(duì)應(yīng)的BOOT.bin文件,可將此文件拷貝到V....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十五章HDMI字符顯示實(shí)驗(yàn)

在HDMI輸出實(shí)驗(yàn)中講解了HDMI顯示原理和顯示方式,本實(shí)驗(yàn)介紹如何使用FPGA實(shí)現(xiàn)字符顯示,通過這....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十六章7寸液晶屏顯示實(shí)驗(yàn)

LCD屏顯示方式從屏幕左上角一點(diǎn)開始,從左向右逐點(diǎn)顯示,每顯示完一行,再回到屏幕的左邊下一行的起始位....

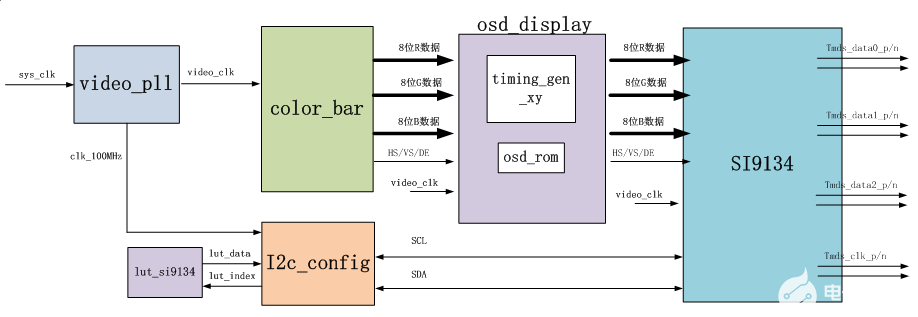

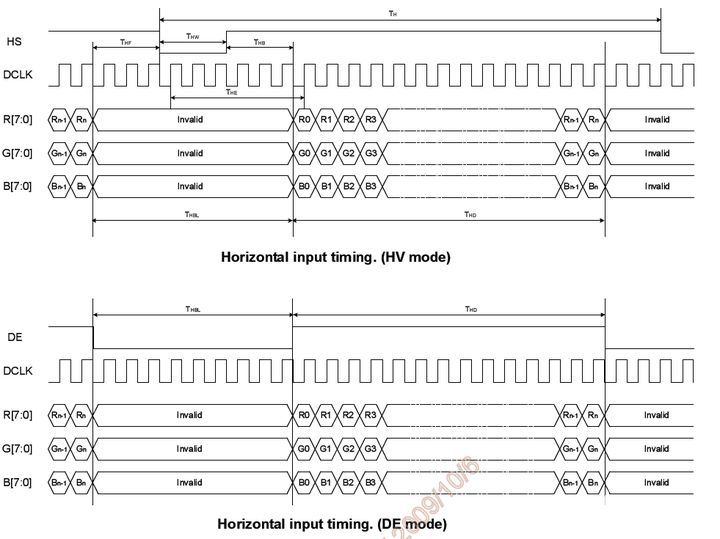

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十四章HDMI輸出實(shí)驗(yàn)

由于開發(fā)板上只有DP可以顯示,但卻是PS端的,PL端沒有HDMI的接口,因此我們采用AN9134的H....

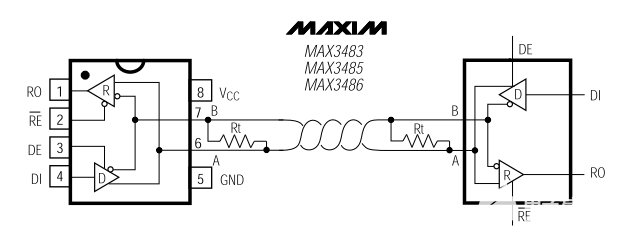

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十三章RS485實(shí)驗(yàn)

RS485與RS422類似,也是采用差分信號(hào)傳輸,但RS485是半雙工傳輸,也就是說,同一時(shí)刻只能有....

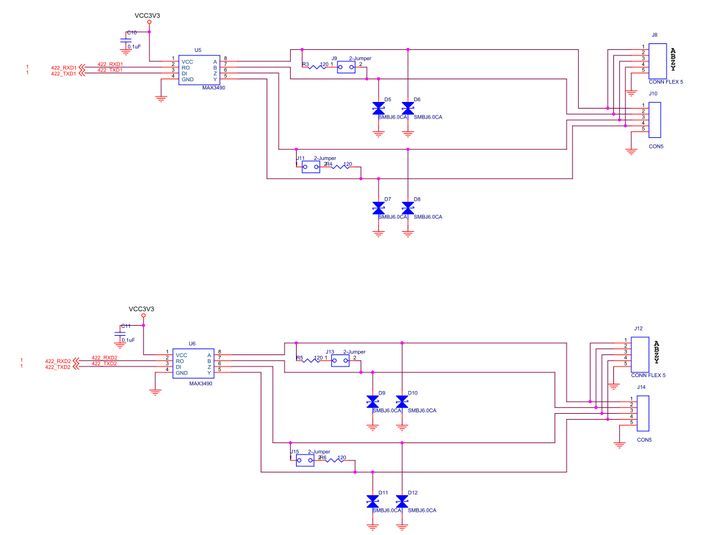

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十二章RS422實(shí)驗(yàn)

本章利用AN3485模塊實(shí)現(xiàn)RS422接口數(shù)據(jù)傳輸。關(guān)于模塊,在前面的RS232實(shí)驗(yàn)中已經(jīng)介紹過,本....

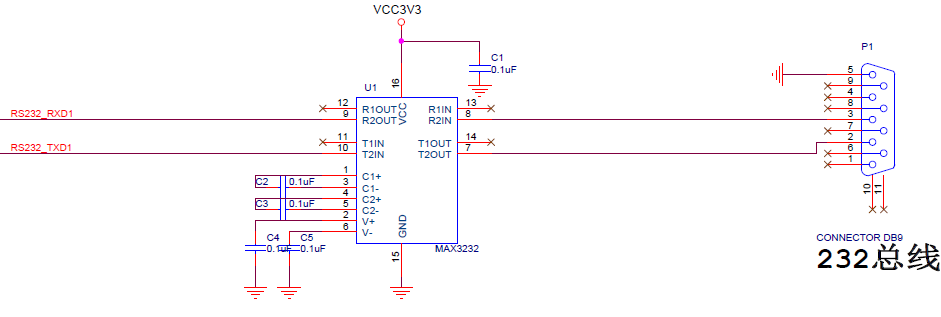

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十一章RS232實(shí)驗(yàn)

AN3485模塊的RS232接口采用MAX3232芯片實(shí)現(xiàn)RS232和+3.3V TTL電平的轉(zhuǎn)換。....

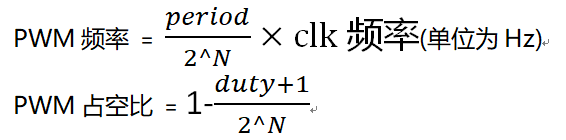

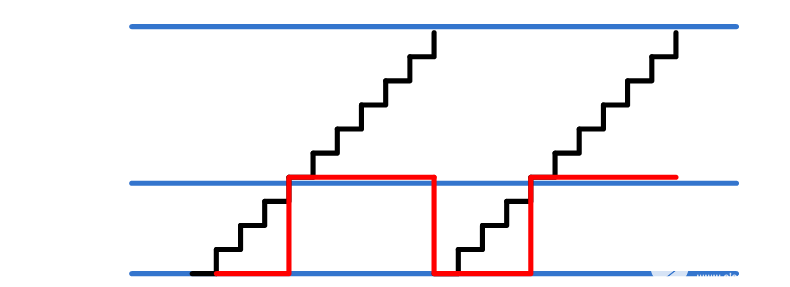

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十章PWM呼吸燈實(shí)驗(yàn)

用一個(gè)N比特的計(jì)數(shù)器,最大值可以表示為2的N次方,最小值0,計(jì)數(shù)器以“period”為步進(jìn)值累加,加....

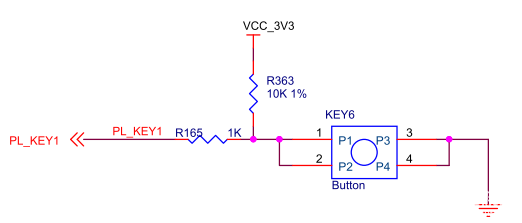

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按鍵實(shí)驗(yàn)

按鍵是FPGA設(shè)計(jì)當(dāng)中最常用也是最簡單的外設(shè),本章通過按鍵檢測實(shí)驗(yàn),檢測開發(fā)板的按鍵功能是否正常,并....

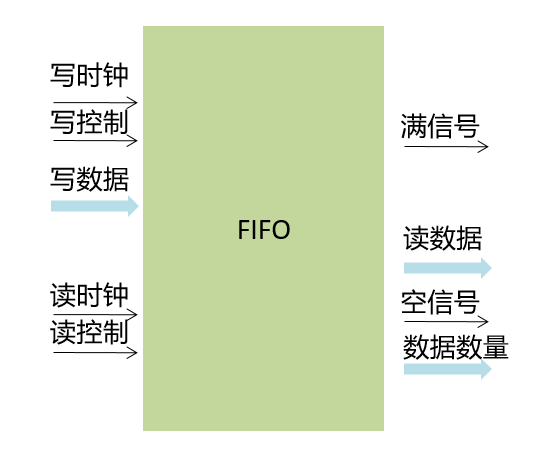

【ZYNQ Ultrascale+ MPSOC FPGA教程】第八章FPGA片內(nèi)FIFO讀寫測試實(shí)驗(yàn)

FIFO: First in, First out代表先進(jìn)的數(shù)據(jù)先出,后進(jìn)的數(shù)據(jù)后出。Xilinx在....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第七章FPGA片內(nèi)ROM測試實(shí)驗(yàn)

既然是ROM,那么我們就必須提前給它準(zhǔn)備好數(shù)據(jù),然后在FPGA實(shí)際運(yùn)行時(shí),我們直接讀取這些ROM中預(yù)....

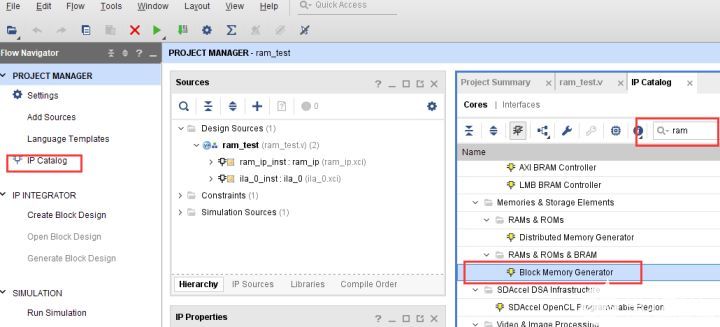

【ZYNQ Ultrascale+ MPSOC FPGA教程】第六章FPGA片內(nèi)RAM讀寫測試實(shí)驗(yàn)

RAM是FPGA中常用的基礎(chǔ)模塊,可廣泛用于緩存數(shù)據(jù)的情況,同樣它也是ROM,F(xiàn)IFO的基礎(chǔ)。本實(shí)驗(yàn)....

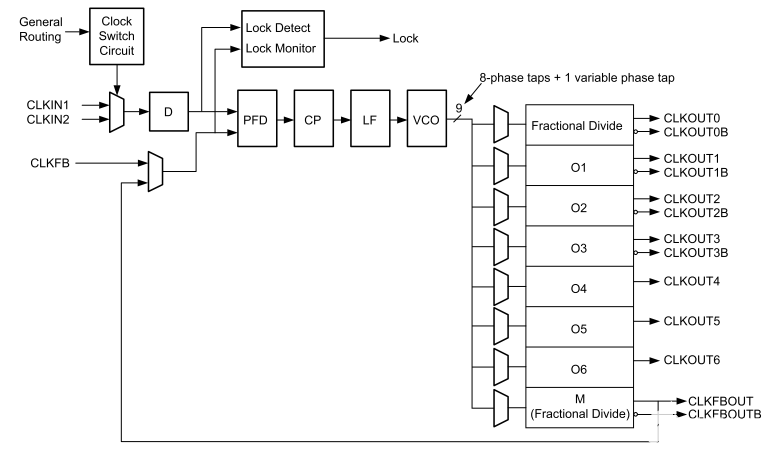

【ZYNQ Ultrascale+ MPSOC FPGA教程】第五章Vivado下PLL實(shí)驗(yàn)

PLL(phase-locked loop),即鎖相環(huán)。是FPGA中的重要資源。由于一個(gè)復(fù)雜的FPG....