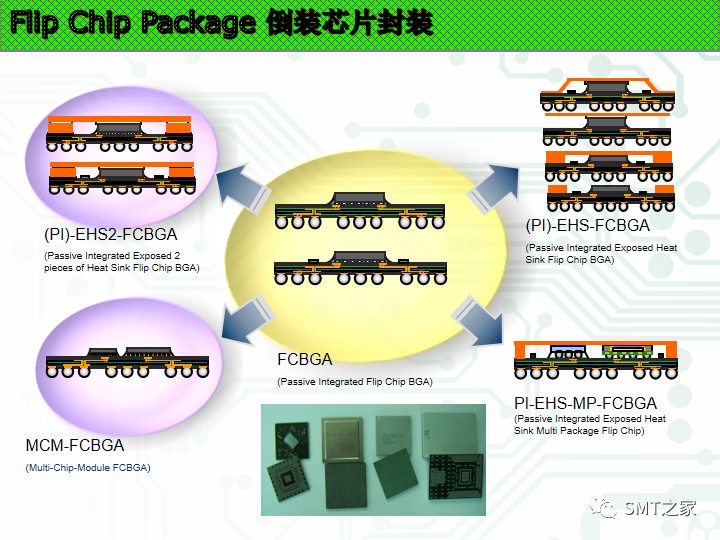

業(yè)界普遍認(rèn)為����,倒裝封裝是傳統(tǒng)封裝和先進(jìn)封裝的分界點(diǎn)�。

2025-05-13 10:01:59 1668

1668

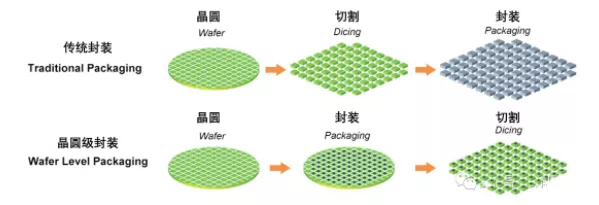

常規(guī)IC封裝需經(jīng)過(guò)將晶圓與IC封裝基板焊接,再將IC基板焊接至普通PCB的復(fù)雜過(guò)程�����。與之不同����,WLP基于IC晶圓,借助PCB制造技術(shù)�,在晶圓上構(gòu)建類(lèi)似IC封裝基板的結(jié)構(gòu),塑封后可直接安裝在普通PCB

2025-05-14 11:08:16 2423

2423

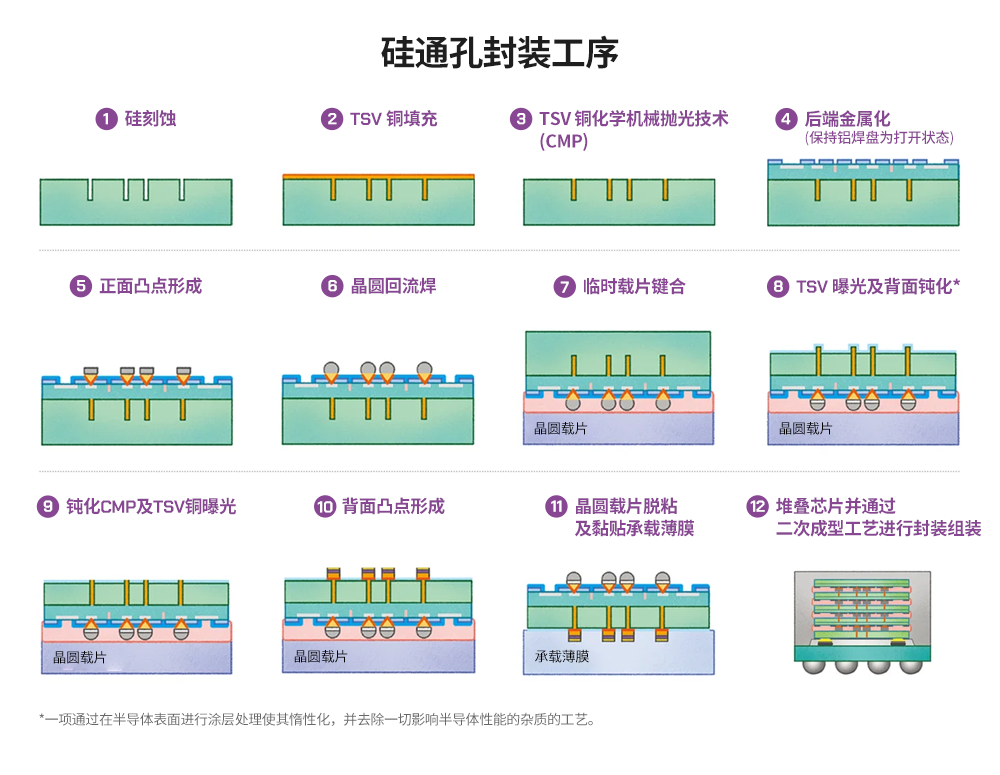

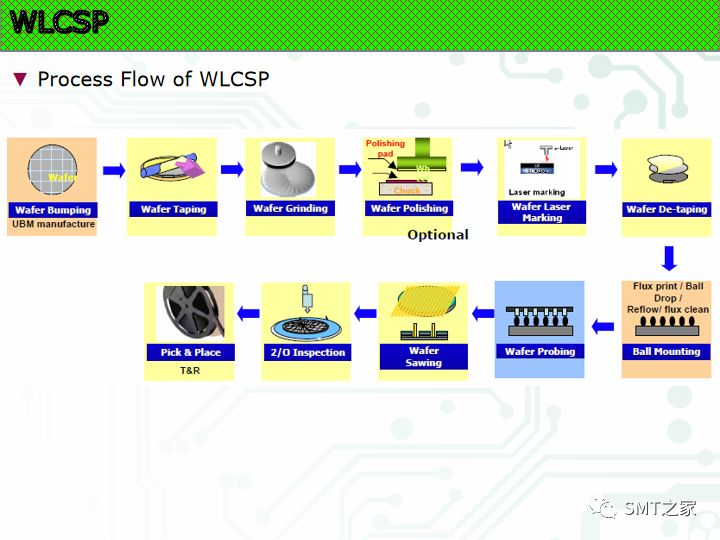

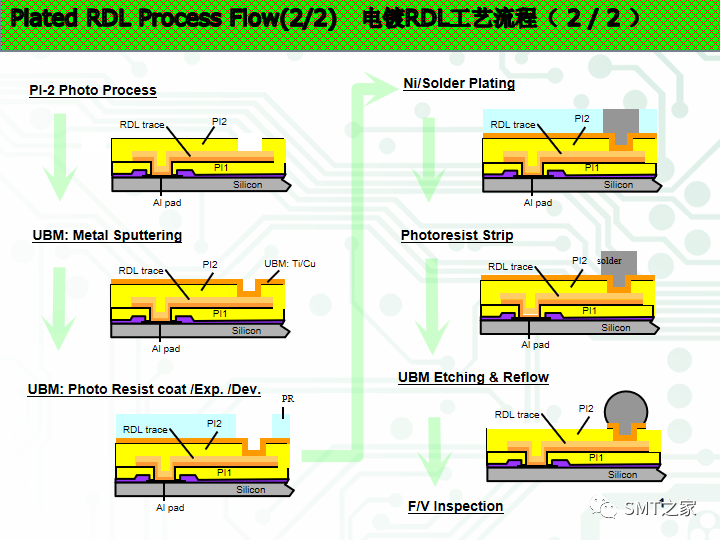

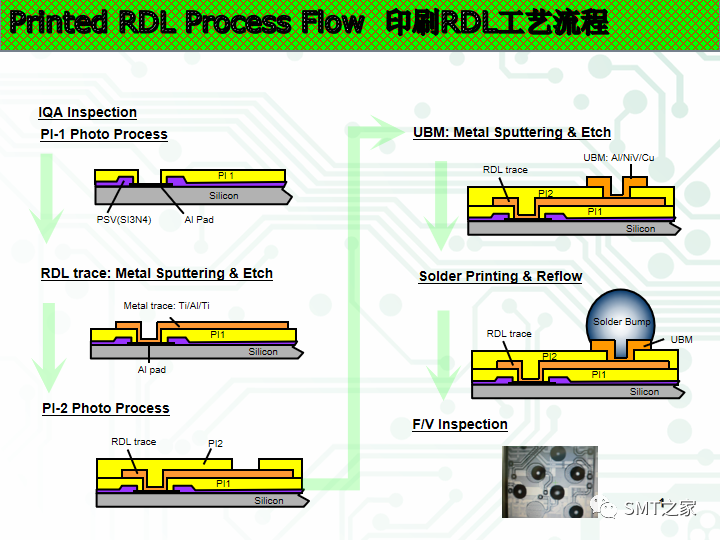

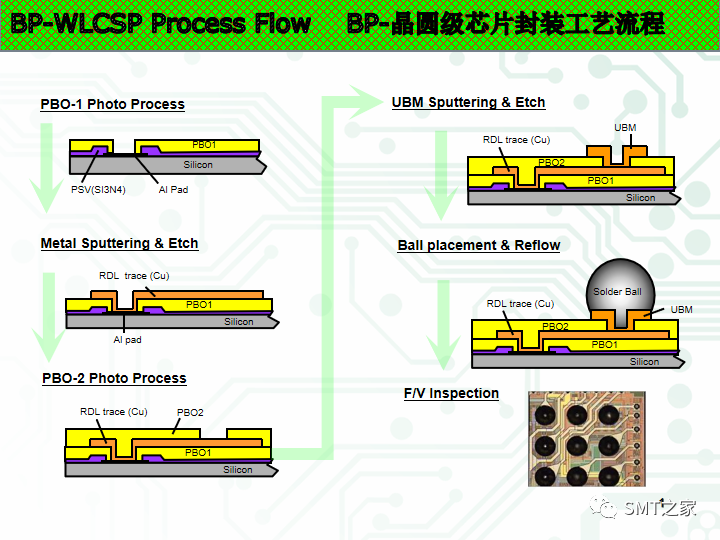

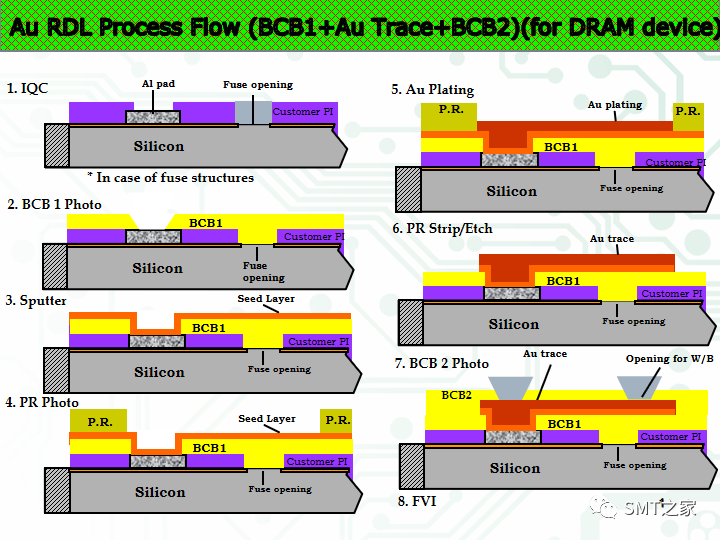

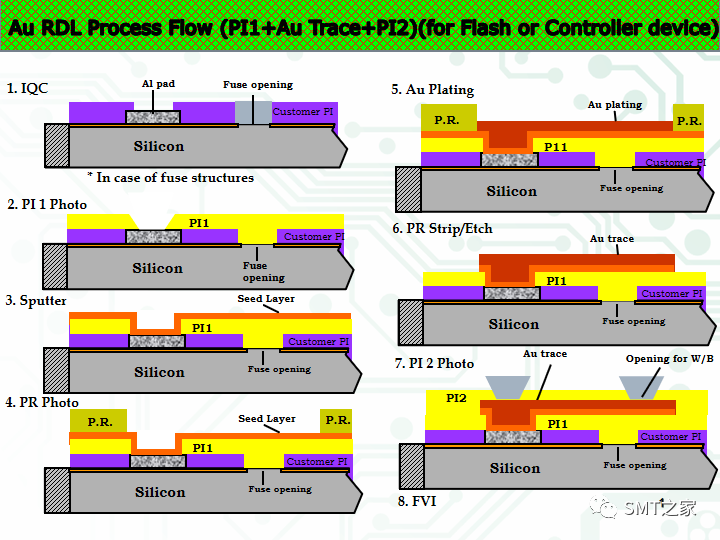

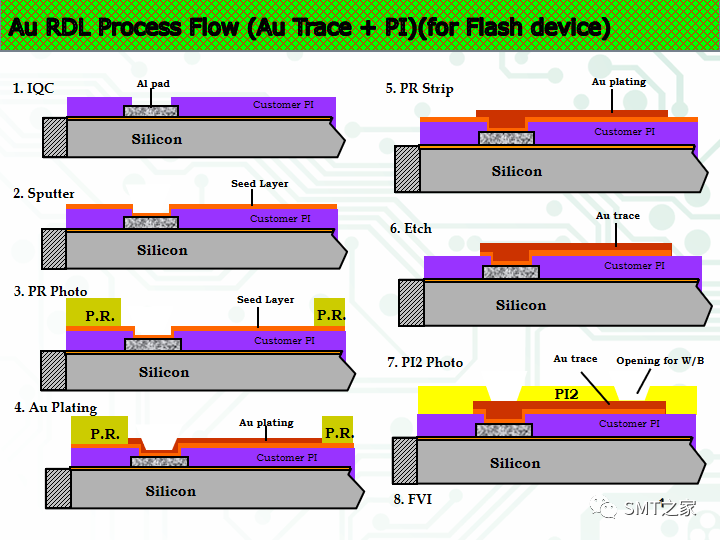

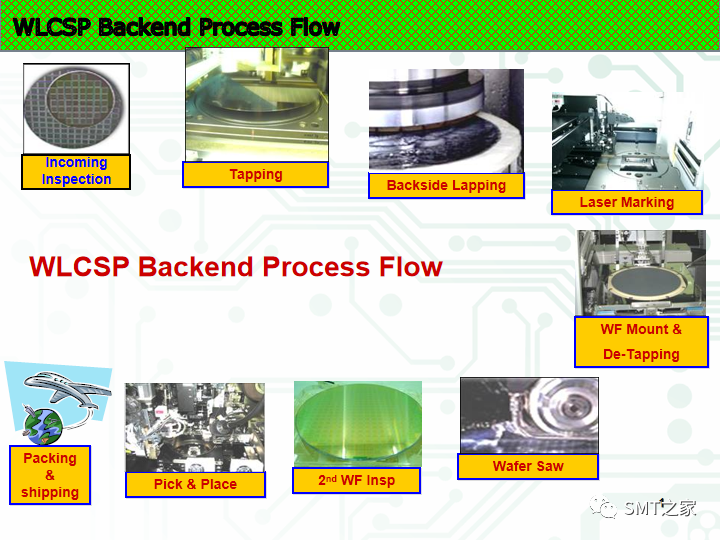

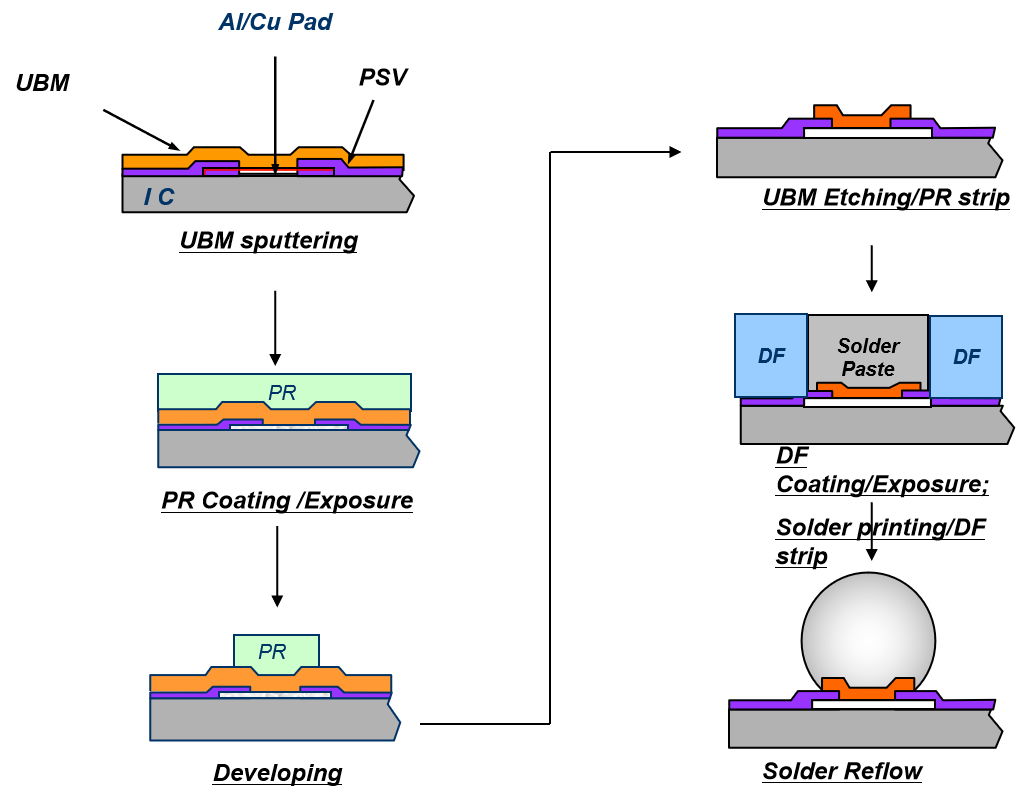

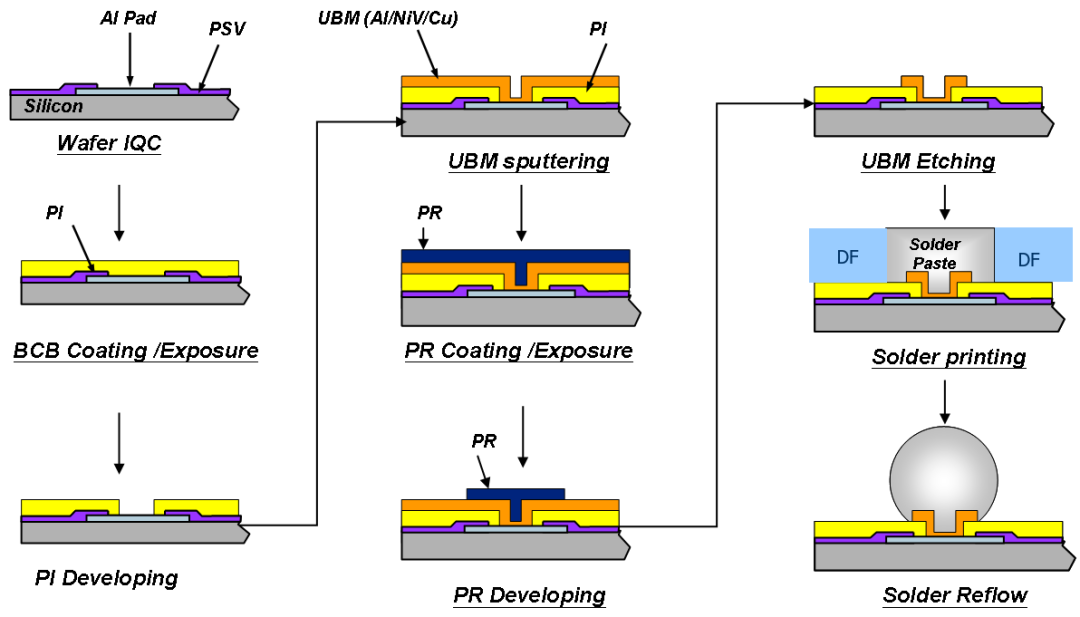

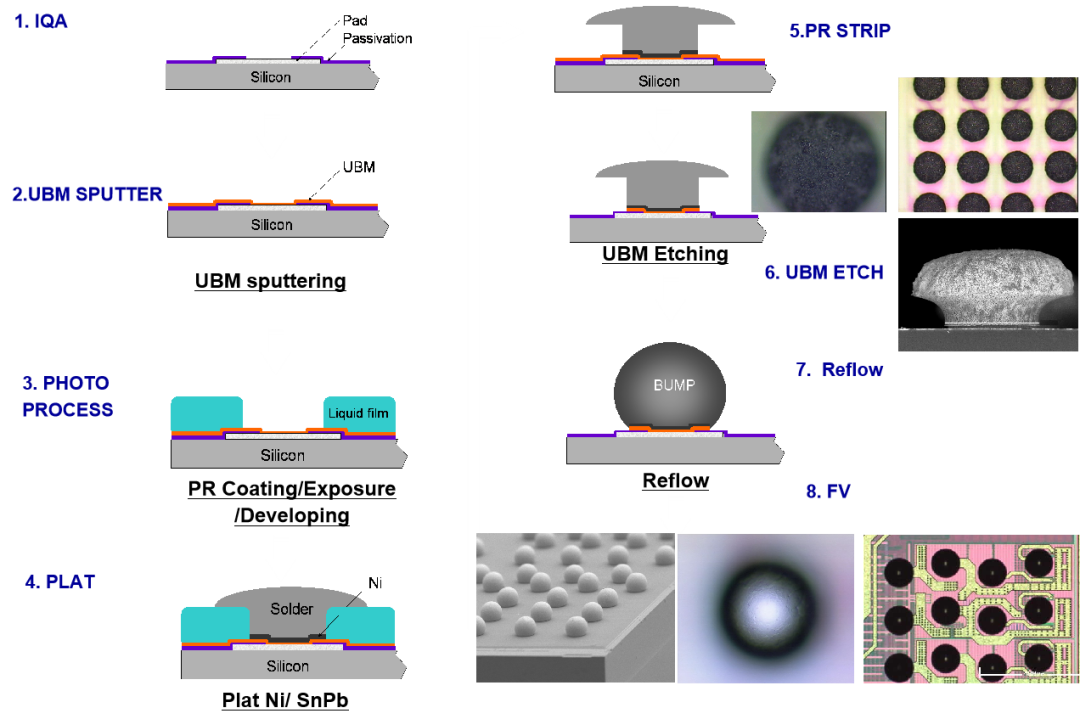

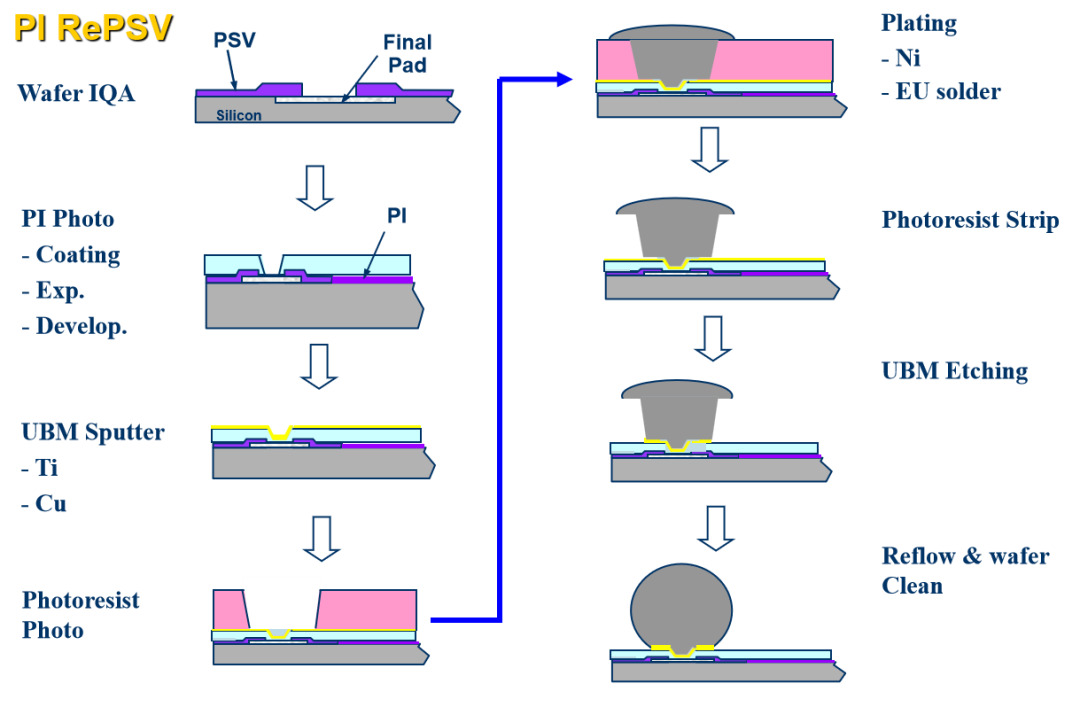

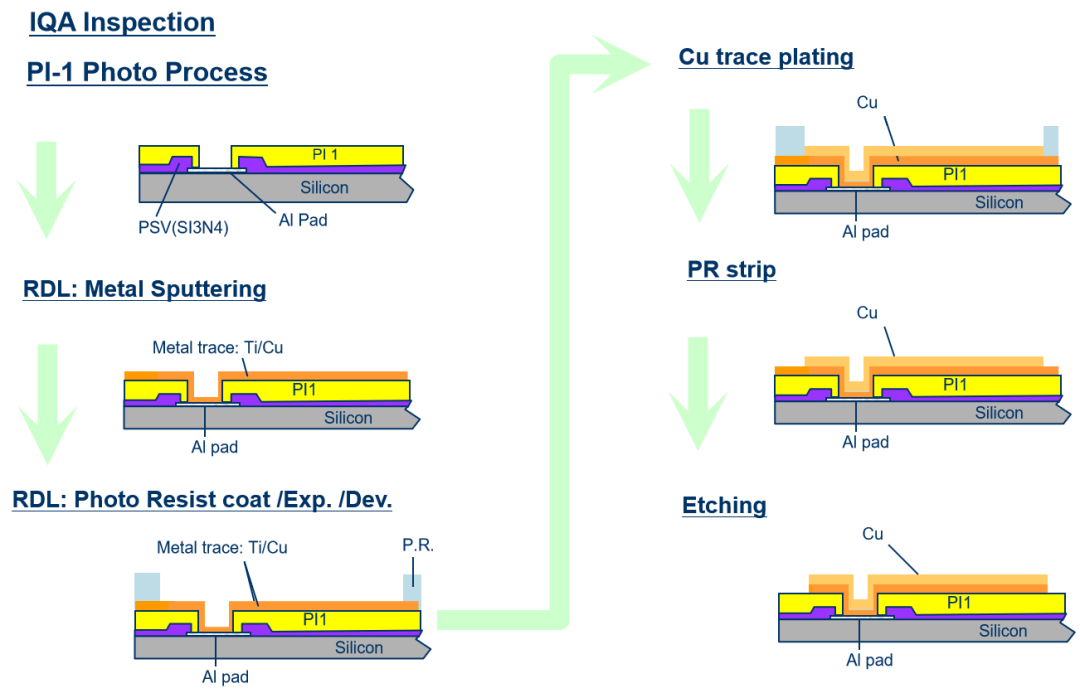

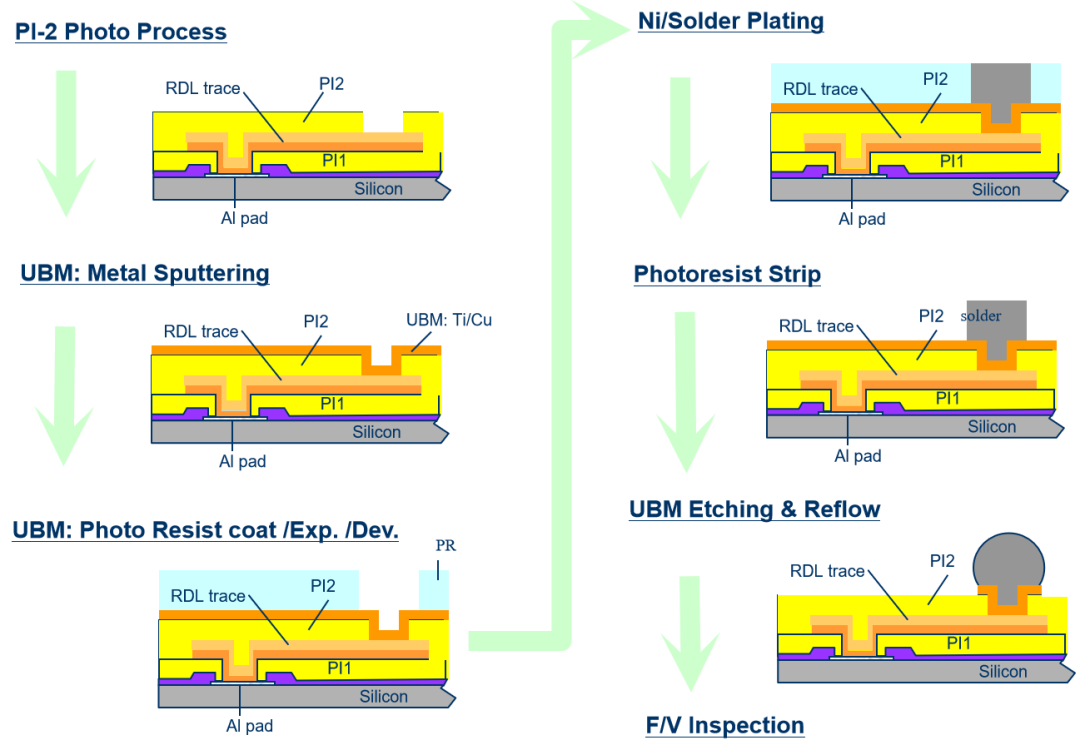

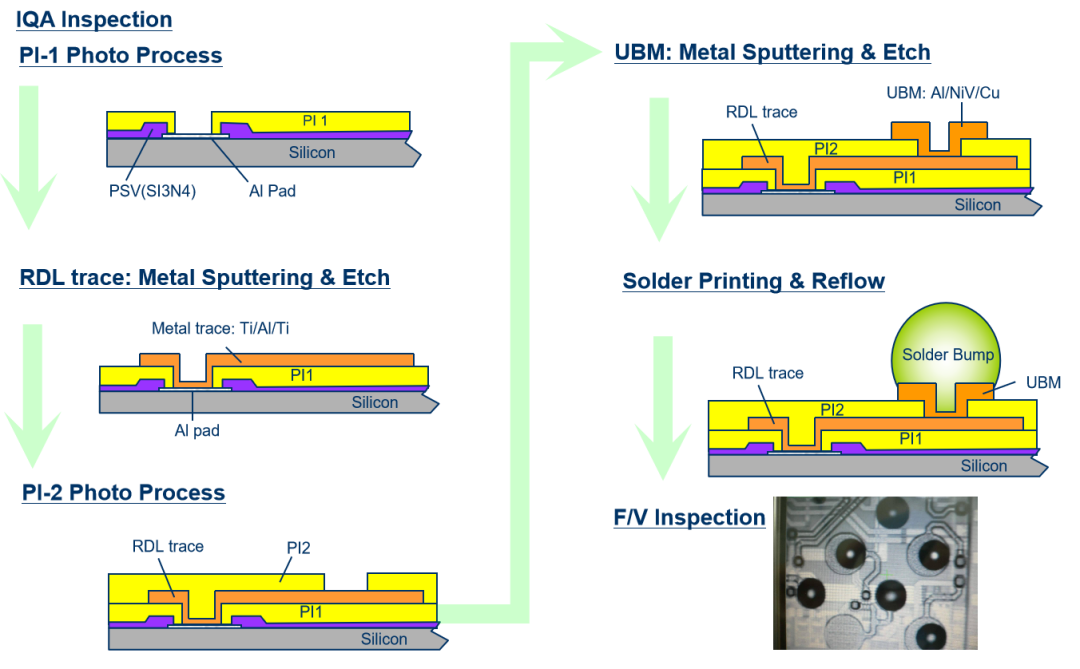

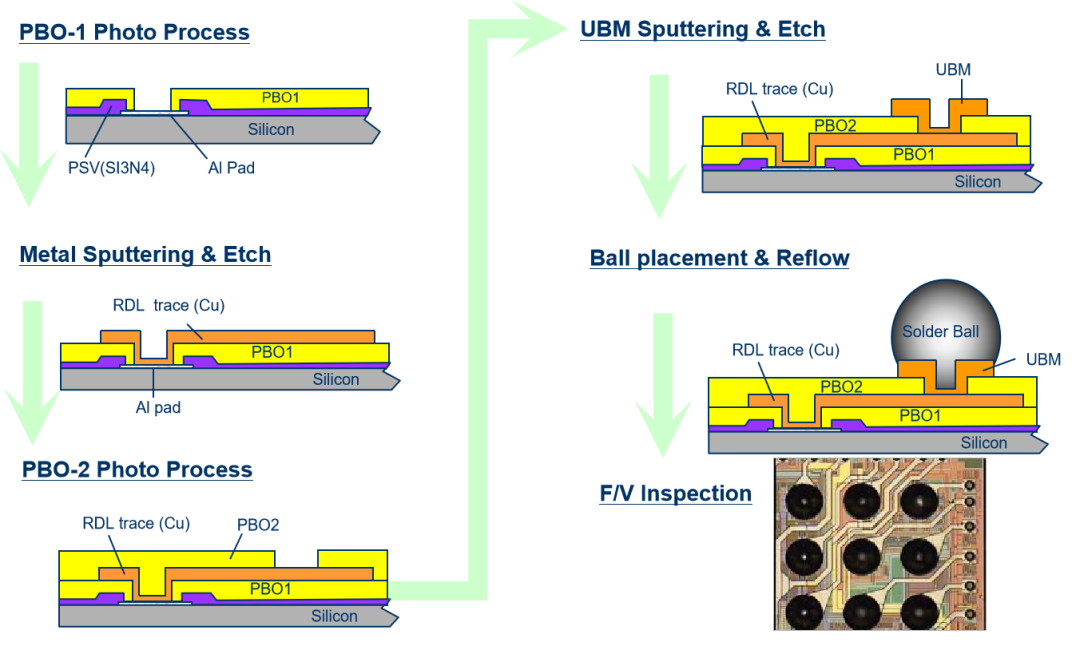

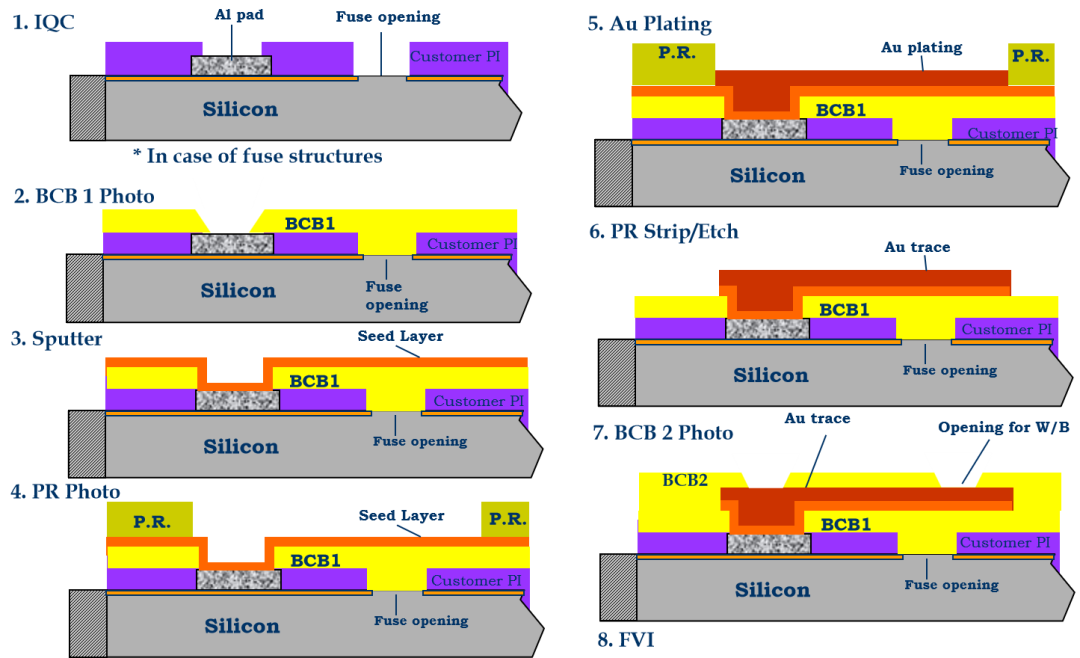

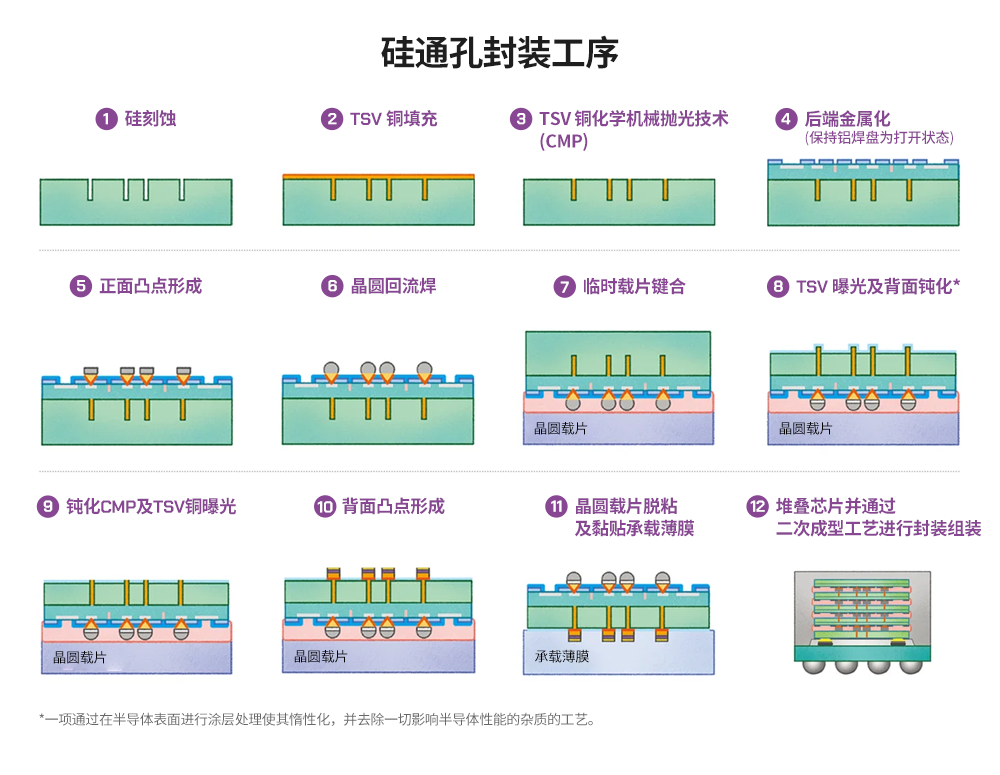

介紹了晶圓級(jí)封裝的基本流程�����。本篇文章將側(cè)重介紹不同晶圓級(jí)封裝方法所涉及的各項(xiàng)工藝����。晶圓級(jí)封裝可分為扇入型晶圓級(jí)芯片封裝(Fan-In WLCSP)���、扇出型晶圓級(jí)芯片封裝(Fan-Out WLCSP

2023-11-08 09:20:19 11649

11649

隨著晶圓級(jí)封裝技術(shù)的不斷提升,眾多芯片設(shè)計(jì)及封測(cè)公司開(kāi)始思考并嘗試采用晶圓級(jí)封裝技術(shù)替代傳統(tǒng)封裝�����。其中HRP(Heat?Re-distribution?Packaging)晶圓級(jí)先進(jìn)封裝工藝技術(shù)

2023-11-30 09:23:24 3833

3833

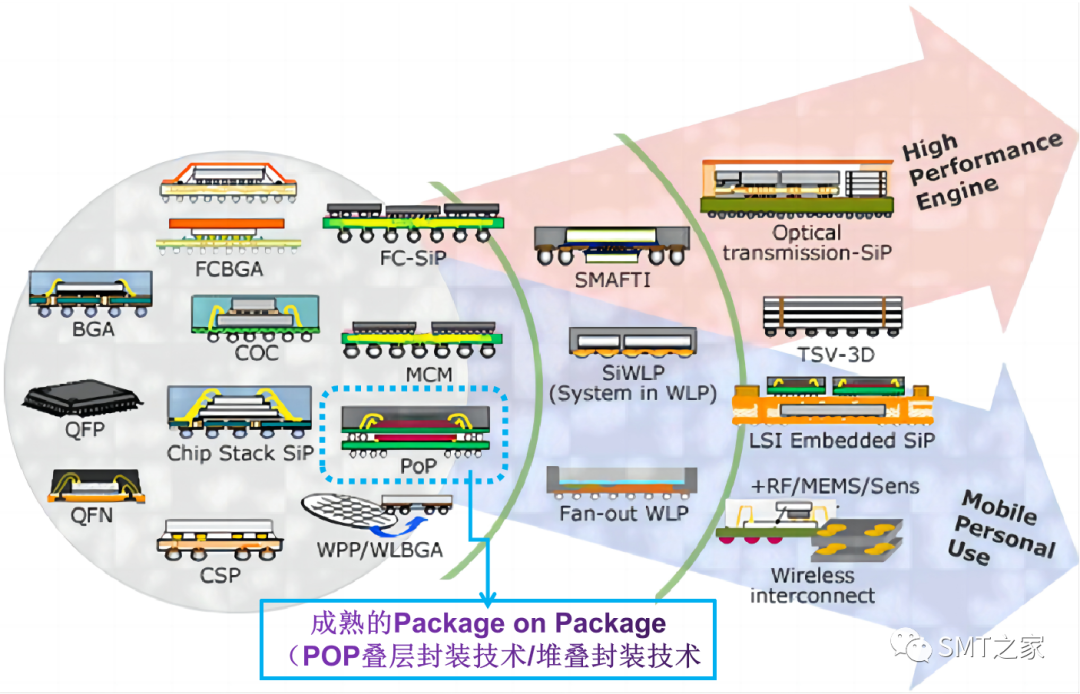

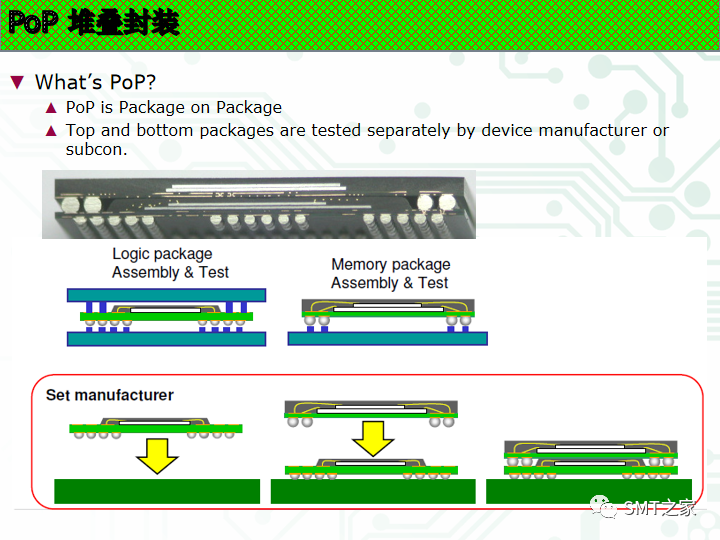

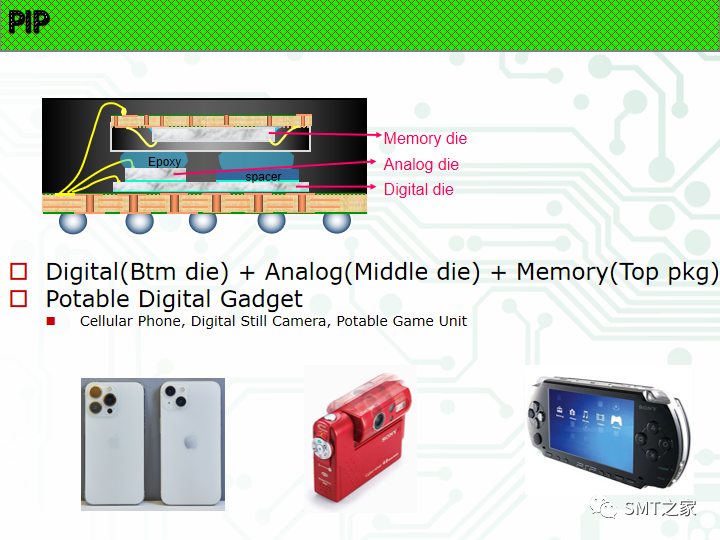

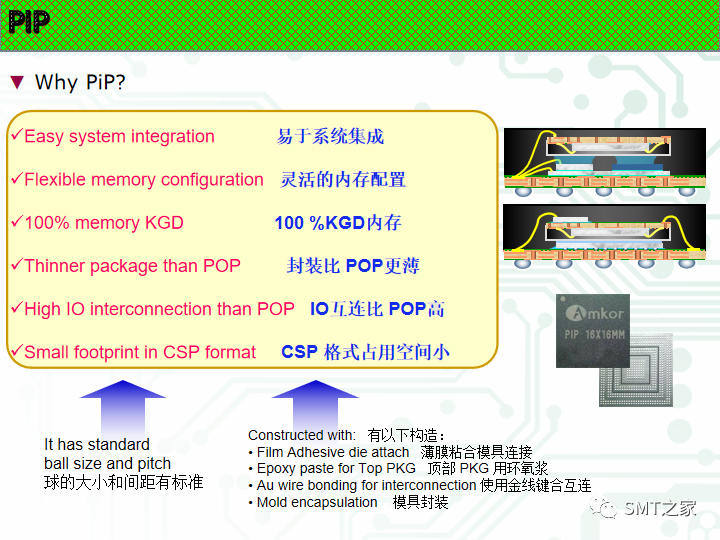

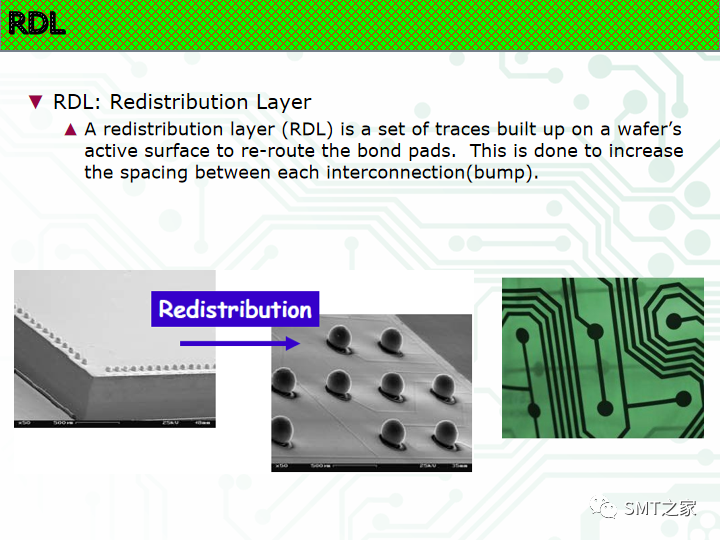

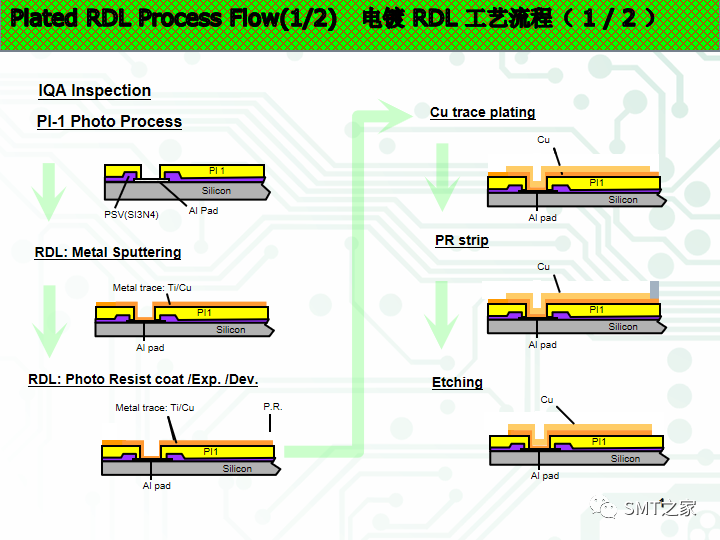

可以應(yīng)用于多種封裝平臺(tái)�����,包括PoP�����、系統(tǒng)級(jí)封裝(SiP)和芯片尺寸封裝( CSP)�。這些優(yōu)勢(shì)來(lái)源于一種稱為再分布層(Redistribution Layer, RDL)的先進(jìn)互連技術(shù)。

2025-01-22 14:57:52 4508

4508

我們看下一個(gè)先進(jìn)封裝的關(guān)鍵概念——晶圓級(jí)封裝(Wafer Level Package����,WLP)。

2025-05-14 10:32:30 1534

1534

晶圓級(jí)扇出封裝(FO-WLP)通過(guò)環(huán)氧樹(shù)脂模塑料(EMC)擴(kuò)展芯片有效面積�,突破了扇入型封裝的I/O密度限制,但其技術(shù)復(fù)雜度呈指數(shù)級(jí)增長(zhǎng)��。

2025-06-05 16:25:57 2152

2152

在功率半導(dǎo)體封裝領(lǐng)域���,晶圓級(jí)芯片規(guī)模封裝技術(shù)正引領(lǐng)著分立功率器件向更高集成度、更低損耗及更優(yōu)熱性能方向演進(jìn)�。

2025-10-21 17:24:13 3875

3875

WLP的命名上還存在分歧。CSP晶片級(jí)技術(shù)非常獨(dú)特���,封裝內(nèi)部并沒(méi)有采用鍵合方式。封裝芯片的命名也存在分歧��。常用名稱有:倒裝芯片(STMicroelectronics和Dalias

2018-08-27 15:45:31

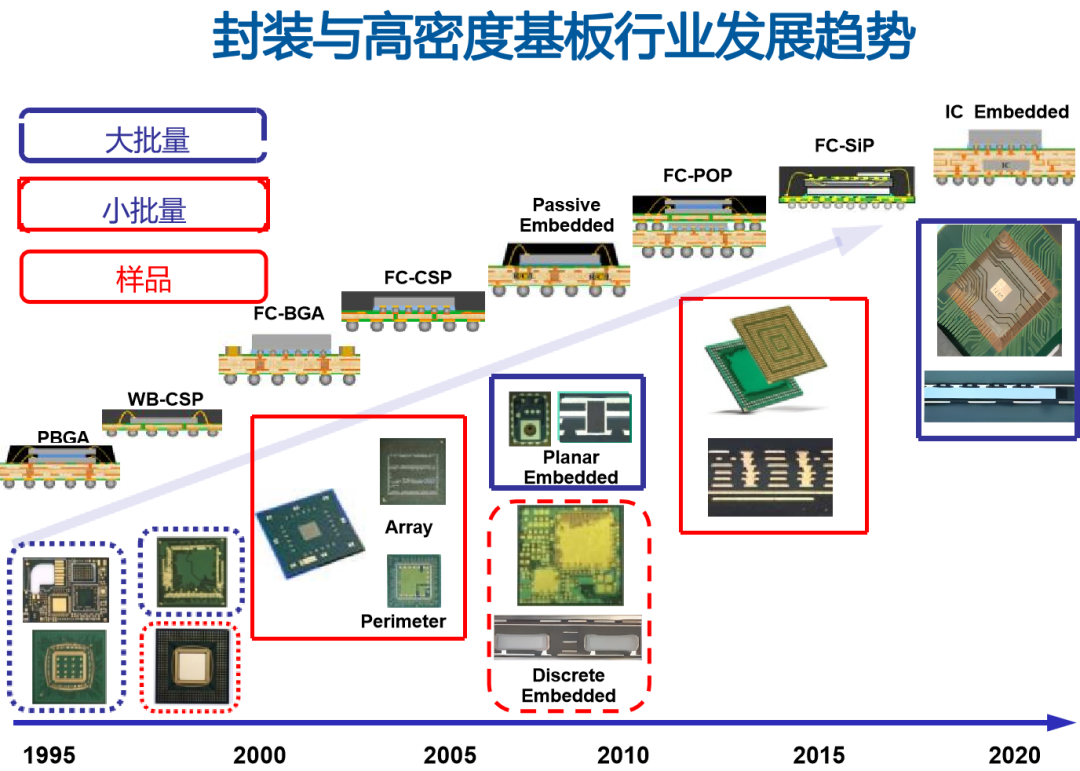

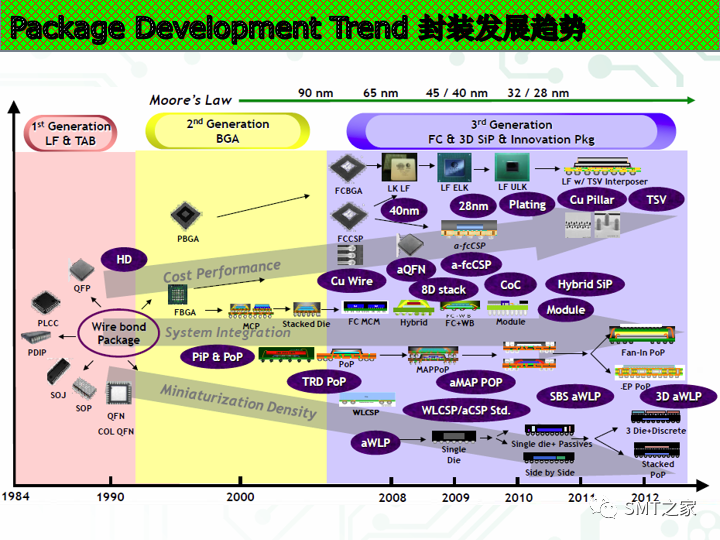

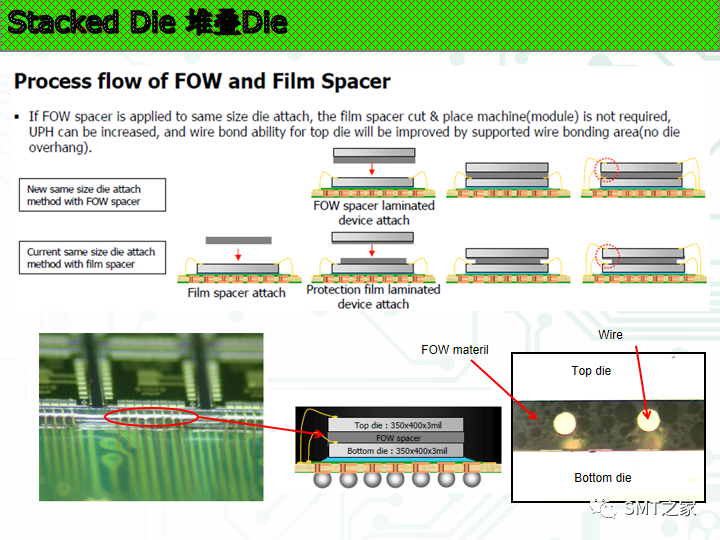

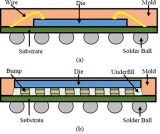

在封裝技術(shù)卜的反映�。提出了目前和可預(yù)見(jiàn)的將來(lái)引線鍵合作為半導(dǎo)體封裝內(nèi)部連接的主流方式與高性能儷成本的倒裝芯片長(zhǎng)期共存,共同和硅片鍵合應(yīng)用在SiP���、MCM�、3D等新型封裝當(dāng)中的預(yù)測(cè)�。1 半導(dǎo)體封裝外部

2018-11-23 17:03:35

有人又將其稱為圓片級(jí)-芯片尺寸封裝(WLP-CSP)����,以晶圓圓片為加工對(duì)象,在晶圓上封裝芯片��。晶圓封裝中最關(guān)鍵的工藝為晶圓鍵合��,即是通過(guò)化學(xué)或物理的方法將兩片晶圓結(jié)合在一起,以達(dá)到密封效果��。如下

2021-02-23 16:35:18

晶圓級(jí)封裝技術(shù)源自于倒裝芯片���。晶圓級(jí)封裝的開(kāi)發(fā)主要是由集成器件制造廠家(IBM)率先啟動(dòng)�。1964年��,美國(guó)IBM公司在其M360計(jì)算器中最先采用了FCOB焊料凸點(diǎn)倒裝芯片器件����。

2020-03-06 09:02:23

晶圓級(jí)封裝類(lèi)型及涉及的產(chǎn)品

2015-07-11 18:21:31

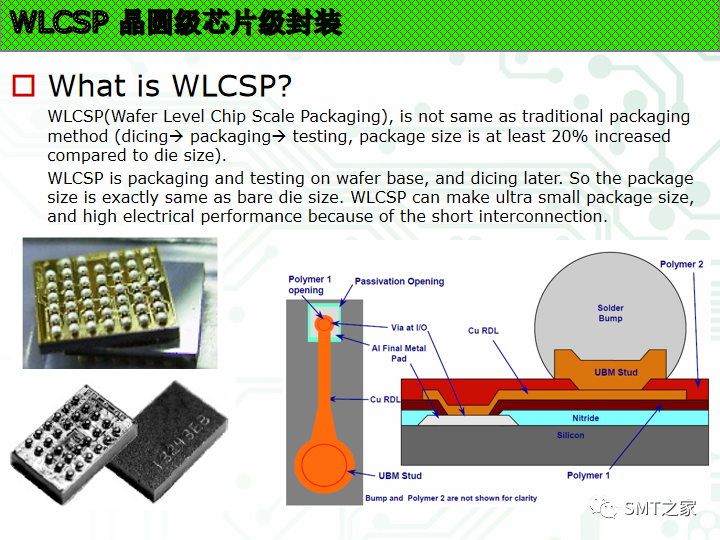

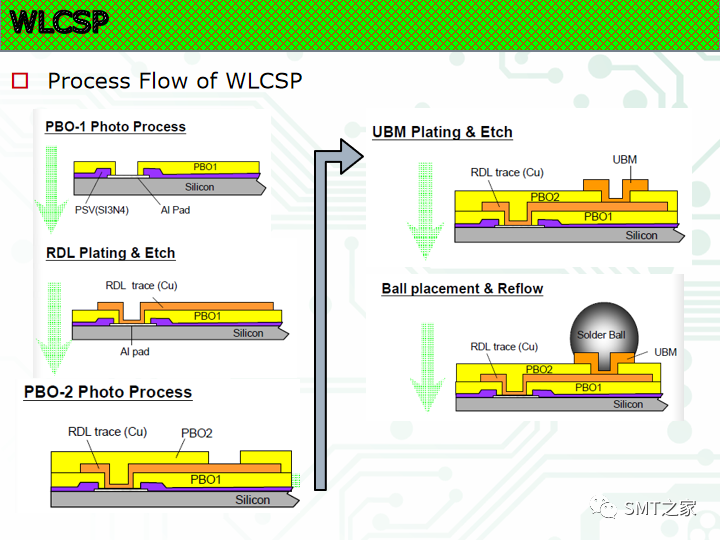

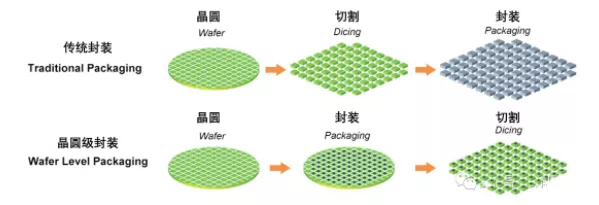

晶圓級(jí)芯片封裝技術(shù)是對(duì)整片晶圓進(jìn)行封裝測(cè)試后再切割得到單個(gè)成品芯片的技術(shù),封裝后的芯片尺寸與裸片一致�����。

2019-09-18 09:02:14

先進(jìn)封裝發(fā)展背景晶圓級(jí)三維封裝技術(shù)發(fā)展

2020-12-28 07:15:50

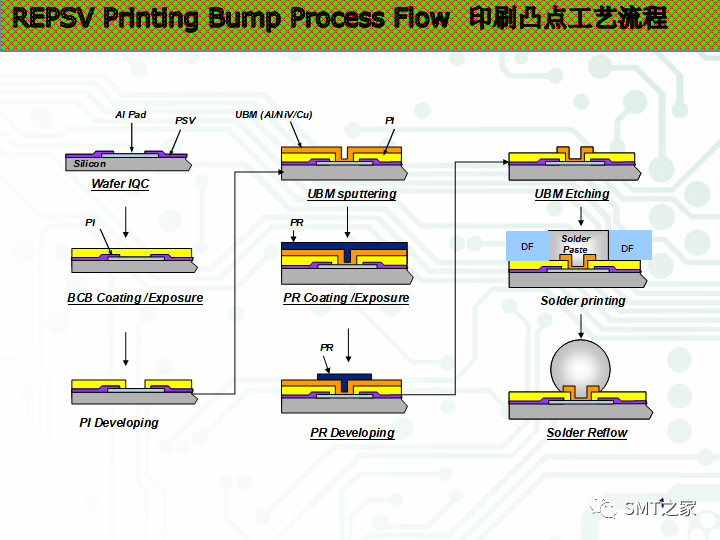

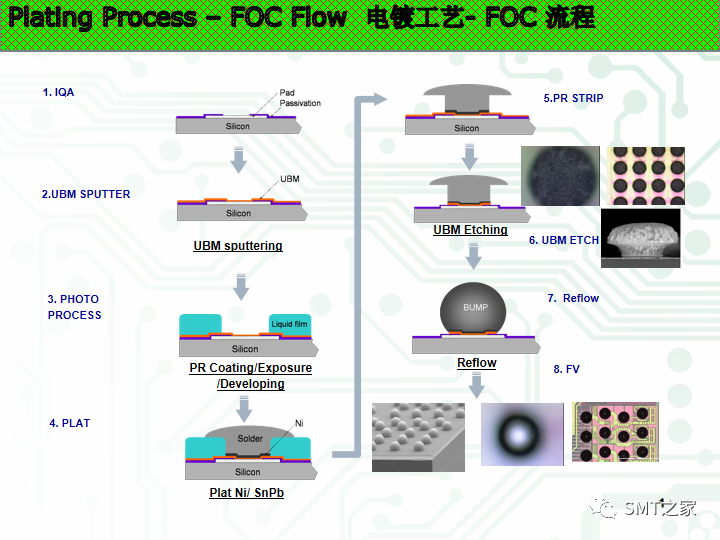

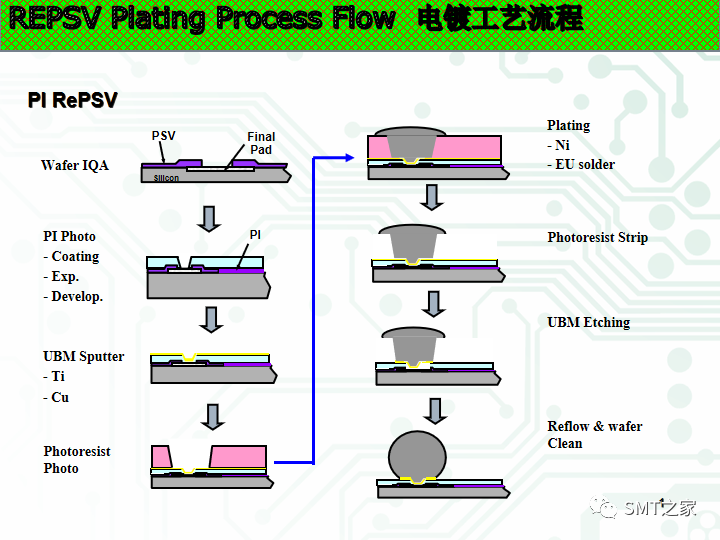

?�! ‰S著越來(lái)越多晶圓焊凸專業(yè)廠家將焊膏印刷工藝用于WLP封裝���,批量壓印技術(shù)開(kāi)始在半導(dǎo)體封裝領(lǐng)域中廣泛普及�。然而,大型EMS企業(yè)也走進(jìn)了WLP領(lǐng)域����。封裝和板卡之間的邊界,以及封裝與組裝工藝之間的邊界日漸模糊����,迫使企業(yè)必須具備晶圓級(jí)和芯片級(jí)工藝技術(shù)來(lái)為客戶服務(wù)`

2011-12-01 14:33:02

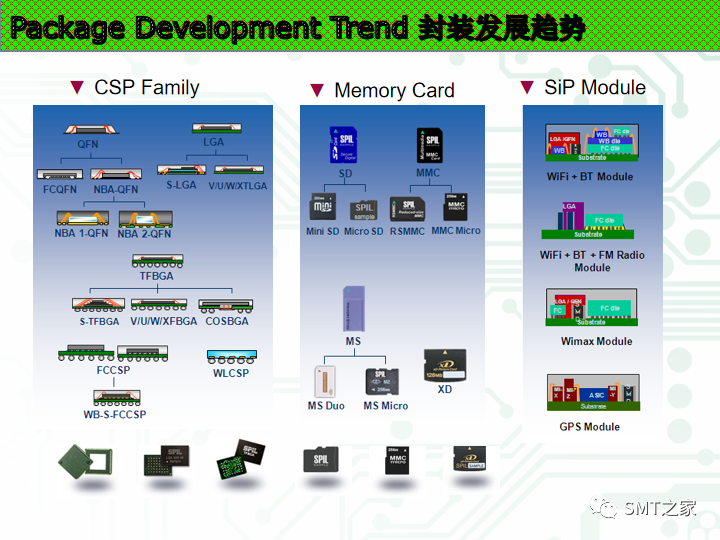

以來(lái)迅速發(fā)展的新型微電子封裝技術(shù),包括焊球陣列封裝(BGA)��、芯片尺寸封裝(CSP)�����、圓片級(jí)封裝(WLP)����、三維封裝(3D)和系統(tǒng)封裝(SIP)等項(xiàng)技術(shù)���。介紹它們的發(fā)展?fàn)顩r和技術(shù)特點(diǎn)。同時(shí)��,敘述了微電子

2023-12-11 01:02:56

Package(晶圓尺寸封裝)��,有別于傳統(tǒng)的單一芯片封裝方式��,WL CSP是將整片晶圓切割為一顆顆的單一芯片����,它號(hào)稱是封裝技術(shù)的未來(lái)主流,已投入研發(fā)的廠商包括FCT���、Aptos�����、卡西歐��、EPIC�、富士通、三菱

2018-11-23 16:59:52

�。 4)Wafer Level Package(晶圓尺寸封裝):有別于傳統(tǒng)的單一芯片封裝方式,WLCSP是將整片晶圓切割為一顆顆的單一芯片���,它號(hào)稱是封裝技術(shù)的未來(lái)主流�,已投入研發(fā)的廠商包括FCT

2017-11-07 15:49:22

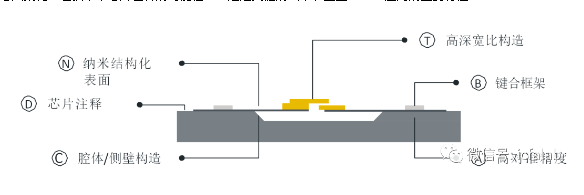

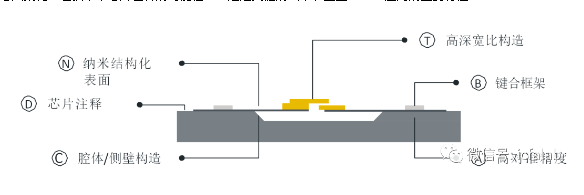

MEMS器件有時(shí)也采用晶圓級(jí)封裝�,并用保護(hù)帽把MEMS密封起來(lái),實(shí)現(xiàn)與外部環(huán)境的隔離或在下次封裝前對(duì)MEMS器件提供移動(dòng)保護(hù)�。這項(xiàng)技術(shù)常常用于慣性芯片的封裝,如陀螺儀和加速度計(jì)�。這樣的封裝步驟是在MEMS

2010-12-29 15:44:12

晶圓級(jí)芯片級(jí)封裝; 49 bumps; 3.29×3.29×0.54mm(包括背面涂層)

2022-12-06 06:06:48

`晶圓級(jí)封裝(WLP)就是在其上已經(jīng)有某些電路微結(jié)構(gòu)(好比古董)的晶片(好比座墊)與另一塊經(jīng)腐蝕帶有空腔的晶片(好比玻璃罩)用化學(xué)鍵結(jié)合在一起�。在這些電路微結(jié)構(gòu)體的上面就形成了一個(gè)帶有密閉空腔的保護(hù)

2011-12-01 13:58:36

設(shè)計(jì)公司���,以及專門(mén)制造的晶圓代工業(yè)者的分別�。設(shè)計(jì)技術(shù)層面上����,芯片設(shè)計(jì)者需要和EDA 開(kāi)發(fā),以及晶圓代工業(yè)者互相密且合作��,能使大規(guī)模的設(shè)計(jì)更有效率���,但是往往芯片設(shè)計(jì)和制造并沒(méi)有形成很好的溝通��,再加上����,先進(jìn)封裝技術(shù)與材料所帶來(lái)的困擾,使得在更進(jìn)一步的芯片模塊進(jìn)展速度上����,有趨緩的現(xiàn)象出現(xiàn)。

2009-10-05 08:11:50

封裝技術(shù)至關(guān)重要�����。衡量一個(gè)芯片封裝技術(shù)先進(jìn)與否的重要指標(biāo)是:芯片面積與封裝面積之比���,這個(gè)比值越接近1越好�。封裝時(shí)主要考慮的因素:芯片面積與封裝面積之比�����,為提高封裝效率�,盡量接近1:1。引腳要盡量短以

2020-02-24 09:45:22

論述了微電子封裝技術(shù)的發(fā)展歷程 發(fā)展現(xiàn)狀及發(fā)展趨勢(shì) 主要介紹了微電子封裝技術(shù)中的芯片級(jí)互聯(lián)技術(shù)與微電子裝聯(lián)技術(shù) 芯片級(jí)互聯(lián)技術(shù)包括引線鍵合技術(shù) 載帶自動(dòng)焊技術(shù) 倒裝芯片技術(shù) 倒裝芯片技術(shù)是目前

2013-12-24 16:55:06

����。如比較小的阻抗值����、較強(qiáng)的抗干擾能力����、較小的信號(hào)失真等等。芯片的封裝技術(shù)經(jīng)歷了好幾代的變遷��,從DIP��、QFP�����、PGA��、BGA到CSP再到MCM�����。技術(shù)指標(biāo)和電器性能一代比一代先進(jìn)���。

2011-10-28 10:51:06

固態(tài)圖像傳感器要求在環(huán)境大氣中得到有效防護(hù)。第一代圖像傳感器安裝在帶玻璃蓋的標(biāo)準(zhǔn)半導(dǎo)體封裝中。這種技術(shù)能使裸片得到很好的密封和異常堅(jiān)固的保護(hù)����,但體積比較龐大,制造成本也比較高�。引入晶圓級(jí)封裝后

2018-12-03 10:19:27

封裝技術(shù)(倒裝芯片接合和柔性載板)正好適用于這個(gè)應(yīng)用。倒裝芯片接合技術(shù)已經(jīng)發(fā)展30多年了�����。此一技術(shù)的優(yōu)點(diǎn)是體積小���、接線密度高�����,而且因?yàn)橐_短而電性得以改善4��。倒裝芯片接合技術(shù)的另一個(gè)優(yōu)勢(shì)��,是能夠?qū)⒍鄠€(gè)

2018-09-11 16:05:39

隨著集成電路設(shè)計(jì)師將更復(fù)雜的功能嵌入更狹小的空間�����,異構(gòu)集成包括器件的3D堆疊已成為混合與連接各種功能技術(shù)的一種更為實(shí)用且經(jīng)濟(jì)的方式����。作為異構(gòu)集成平臺(tái)之一,高密度扇出型晶圓級(jí)封裝技術(shù)正獲得越來(lái)越多

2020-07-07 11:04:42

了封裝由單個(gè)小芯片級(jí)轉(zhuǎn)向硅圓片級(jí)(wafer level)封裝的變革����,由此引出系統(tǒng)級(jí)芯片SOC(System On Chip)和電腦級(jí)芯片PCOC(PC On Chip)?����! ‰S著CPU和其他ULSI電路的進(jìn)步����,集成電路的封裝形式也將有相應(yīng)的發(fā)展,而封裝形式的進(jìn)步又將反過(guò)來(lái)促成芯片技術(shù)向前發(fā)展����。

2018-09-03 09:28:18

SRAM中晶圓級(jí)芯片級(jí)封裝的需求

2020-12-31 07:50:40

復(fù)習(xí)與思考題10 第11章 封裝可靠性工程 第12章 封裝過(guò)程中的缺陷分析 第13章 先進(jìn)封裝技術(shù) 附錄A封裝設(shè)備簡(jiǎn)介 A.1 前段操作 A.1.1 貼膜 A.1.2 晶圓背面研磨 A.1.3 烘烤 A.1.4 上片 A.1.5 去膜

2012-01-13 13:59:52

晶圓級(jí)封裝產(chǎn)業(yè)(WLP),晶圓級(jí)封裝產(chǎn)業(yè)(WLP)是什么意思

一、晶圓級(jí)封裝(Wafer Level Packaging)簡(jiǎn)介 晶圓級(jí)封裝(WLP�����,Wafer Level Package) 的一般定

2010-03-04 11:35:01 46790

46790 微芯科技晶圓級(jí)芯片封裝和TO-92封裝

Microchip Technology Inc.(美國(guó)微芯科技公司)宣布推出單I/O總線UNI/O EEPROM器件并且開(kāi)始供貨����,除了采用3引腳SOT-23封裝

2010-04-08 14:26:25 2858

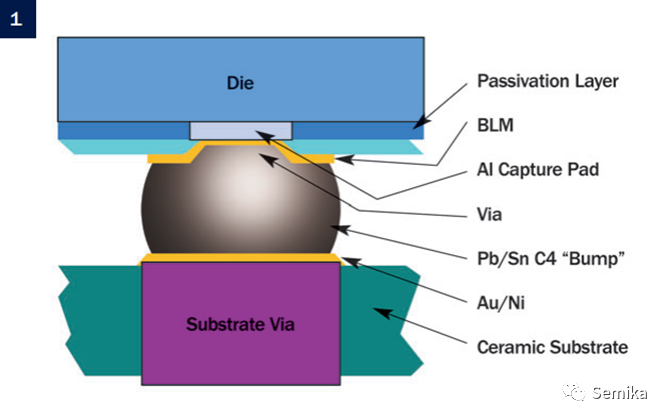

2858 隨著倒裝芯片封裝在成本和性能上的不斷改進(jìn)�, 倒裝芯片 技術(shù)正在逐步取代引線鍵合的位置。倒裝芯片的基本概念就是拿來(lái)一顆芯片���,在連接點(diǎn)位置放上導(dǎo)電的凸點(diǎn)��,將該面翻轉(zhuǎn)���,有

2011-10-19 11:42:55 5575

5575 芯片級(jí)封裝介紹本應(yīng)用筆記提供指引使用與PCB安裝設(shè)備相關(guān)的芯片級(jí)封裝�����。包括系統(tǒng)的PCB布局信息制造業(yè)工程師和制造工藝工藝工程師。 包概述 倒裝芯片CSP的包概述半導(dǎo)體封裝提供的芯片級(jí)封裝代表最小

2017-03-31 10:57:32 45

45 超級(jí)CSP——讓倒裝芯片獲得最大可靠性一種晶圓片級(jí)封裝

2017-09-14 11:31:37 22

22 江蘇中科智芯集成電路晶圓級(jí)封裝芯片項(xiàng)目正在緊鑼密鼓推進(jìn)�。

2019-07-26 14:15:51 5106

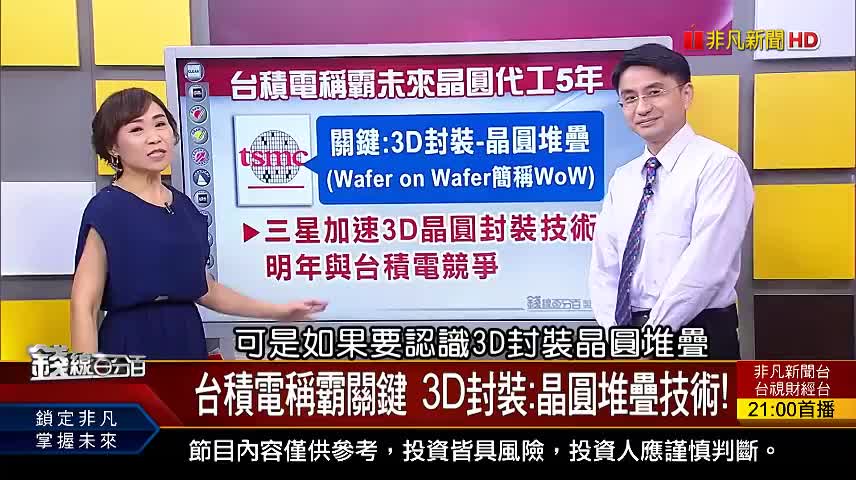

5106 即將于本周舉行線上法人說(shuō)明會(huì)的晶圓代工龍頭臺(tái)積電���,在日前繳出2020年3月?tīng)I(yíng)收創(chuàng)下歷史單月新高����,累計(jì)首季營(yíng)收將能優(yōu)于預(yù)期的亮麗成績(jī)之后�����,現(xiàn)在又傳出在晶圓級(jí)封裝技術(shù)上再有新的突破�,也就是針對(duì)高效能運(yùn)算

2020-04-13 16:11:47 25288

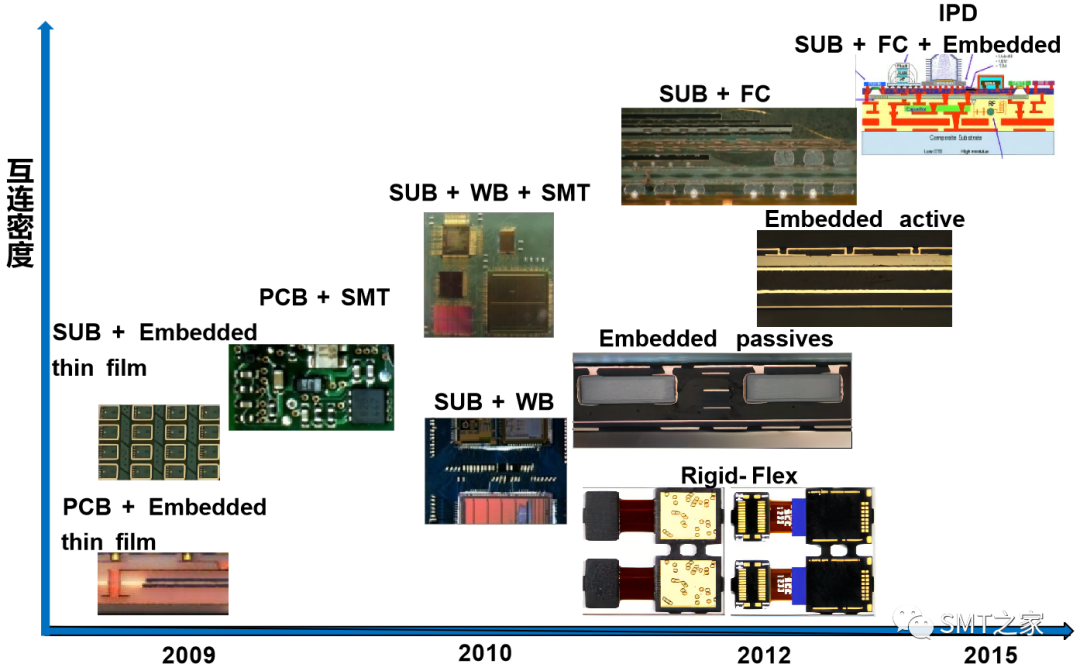

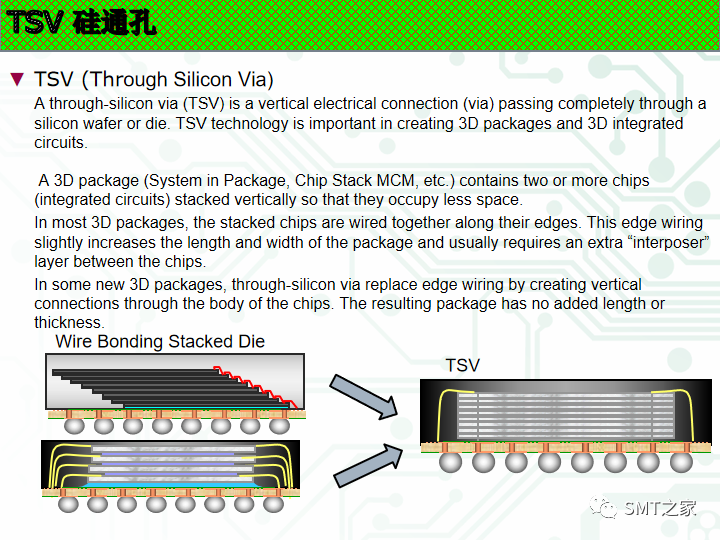

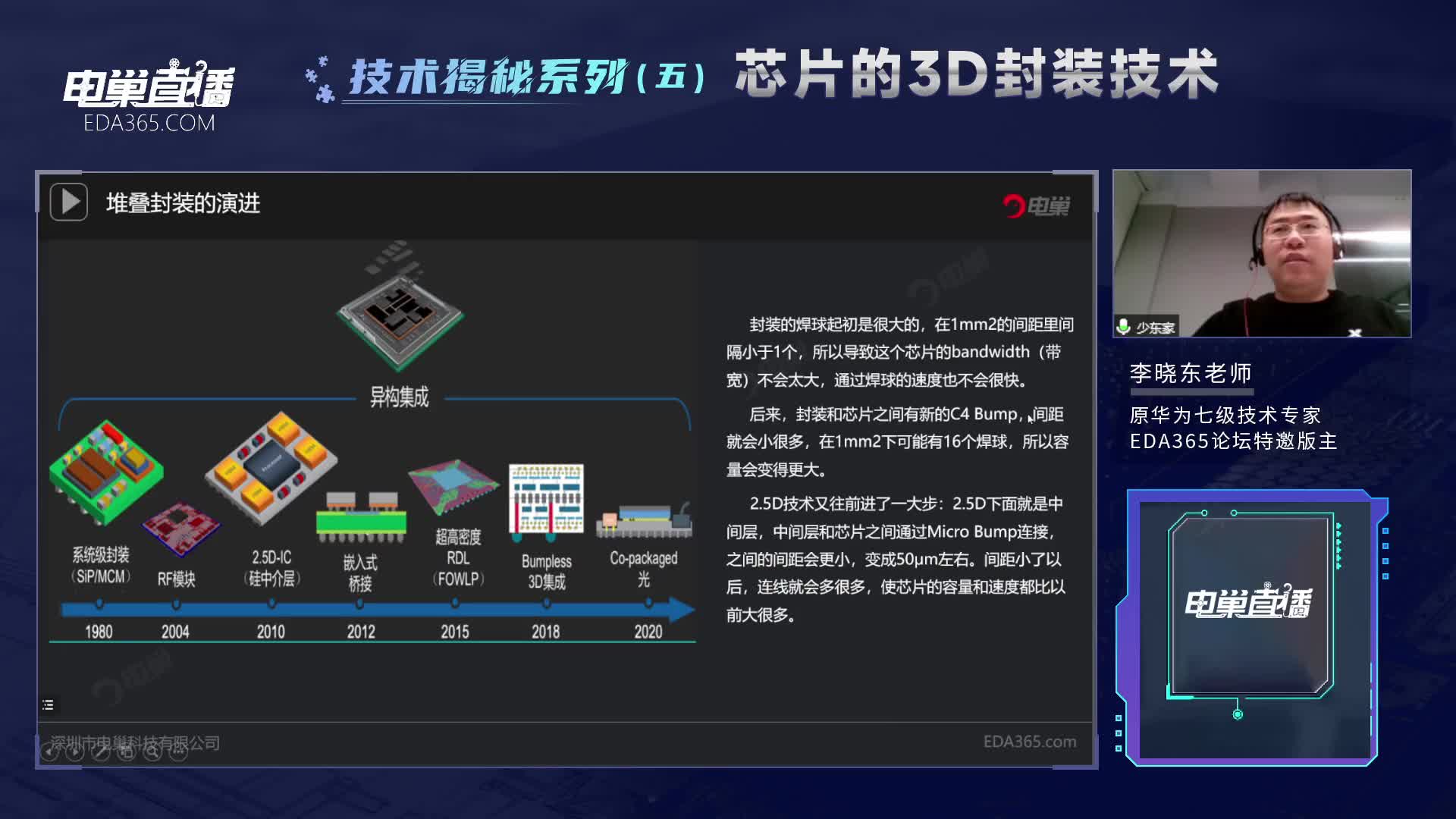

25288 技術(shù)發(fā)展方向 半導(dǎo)體產(chǎn)品在由二維向三維發(fā)展,從技術(shù)發(fā)展方向半導(dǎo)體產(chǎn)品出現(xiàn)了系統(tǒng)級(jí)封裝(SiP)等新的封裝方式��,從技術(shù)實(shí)現(xiàn)方法出現(xiàn)了倒裝(FlipChip)���,凸塊(Bumping)��,晶圓級(jí)封裝(Waferlevelpackage)��,2.5D封裝(interposer�����,RDL等)�,3D封裝(TSV)等先進(jìn)封裝技術(shù)。

2020-10-12 11:34:36 19530

19530

一���、技術(shù)發(fā)展方向 半導(dǎo)體產(chǎn)品在由二維向三維發(fā)展�,從技術(shù)發(fā)展方向半導(dǎo)體產(chǎn)品出現(xiàn)了系統(tǒng)級(jí)封裝(SiP)等新的封裝方式���,從技術(shù)實(shí)現(xiàn)方法出現(xiàn)了倒裝(FlipChip)����,凸塊(Bumping)��,晶圓級(jí)封裝

2020-10-21 11:03:11 32866

32866

摩爾定律在晶圓工藝制程方面已是強(qiáng)弩之末���,此時(shí)先進(jìn)的封裝技術(shù)拿起了接力棒����。扇出型晶圓級(jí)封裝(FOWLP)等先進(jìn)技術(shù)可以提高器件密度���、提升性能�����,并突破芯片I/O數(shù)量的限制�。然而,要成功利用這類(lèi)技術(shù)��,在芯片設(shè)計(jì)之初就要開(kāi)始考慮其封裝���。

2020-11-12 16:55:39 1147

1147 作為華天集團(tuán)晶圓級(jí)先進(jìn)封裝基地,華天昆山2008年6月落戶昆山開(kāi)發(fā)區(qū)�����,研發(fā)的晶圓級(jí)傳感器封裝技術(shù)�����、扇出型封裝技術(shù)��、超薄超小型晶圓級(jí)封裝����、晶圓級(jí)無(wú)源器件制造技術(shù)目前已達(dá)到世界領(lǐng)先水平。

2021-01-09 10:16:09 5508

5508 在傳統(tǒng)晶圓封裝中��,是將成品晶圓切割成單個(gè)芯片���,然后再進(jìn)行黏合封裝�。不同于傳統(tǒng)封裝工藝,晶圓級(jí)封裝是在芯片還在晶圓上的時(shí)候就對(duì)芯片進(jìn)行封裝����,保護(hù)層可以黏接在晶圓的頂部或底部,然后連接電路��,再將晶圓切成單個(gè)芯片����。

2022-04-06 15:24:19 12071

12071 晶圓級(jí)封裝技術(shù)可定義為:直接在晶圓上進(jìn)行大部分或全部的封裝�����、測(cè)試程序��,然后再進(jìn)行安裝焊球并切割��,從而產(chǎn)出一顆顆的IC成品單元���。

2022-07-10 11:23:51 2215

2215 許多MEMS器件需要保護(hù)�����,以免受到外部環(huán)境的影響��,或者只能在受控氣氛或真空下運(yùn)行�����。當(dāng)今MEMS器件與CMOS芯片的高度集成���,還需要專門(mén)用于MEMS器件的先進(jìn)晶圓級(jí)封裝解決方案����。

2022-07-15 12:36:01 5041

5041

倒裝芯片 CSP 封裝

2022-11-14 21:07:58 22

22 采用了先進(jìn)的設(shè)計(jì)思路和先進(jìn)的集成工藝����、縮短引線互連長(zhǎng)度����,對(duì)芯片進(jìn)行系統(tǒng)級(jí)封裝的重構(gòu),并且能有效提高系統(tǒng)功能密度的封裝?,F(xiàn)階段的先進(jìn)封裝是指:倒裝焊(FlipChip)、晶圓級(jí)封裝(WLP)����、2.5D封裝(Interposer�、RDL)��、3D封裝(TSV)

2023-01-13 10:58:41 2298

2298 晶圓級(jí)封裝(Wafer Level Packaging����,縮寫(xiě)WLP)是一種先進(jìn)的封裝技術(shù),因其具有尺寸小����、電性能優(yōu)良、散熱好��、成本低等優(yōu)勢(shì)��,近年來(lái)發(fā)展迅速�����。根據(jù)Verified Market

2023-02-24 09:35:05 3178

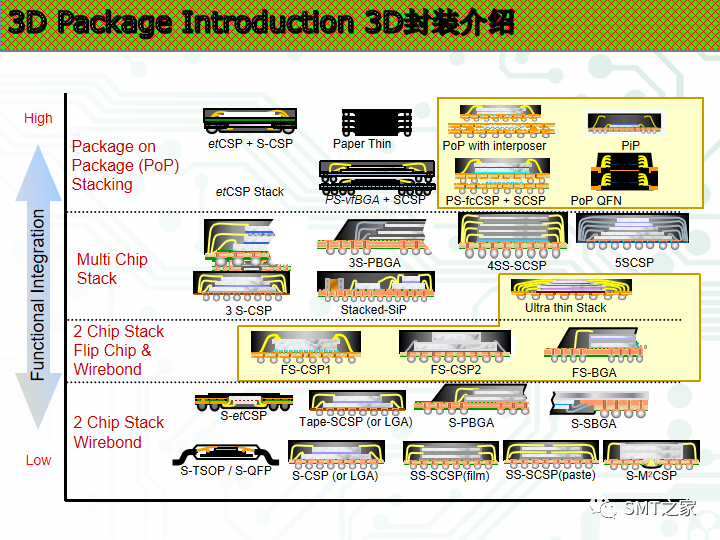

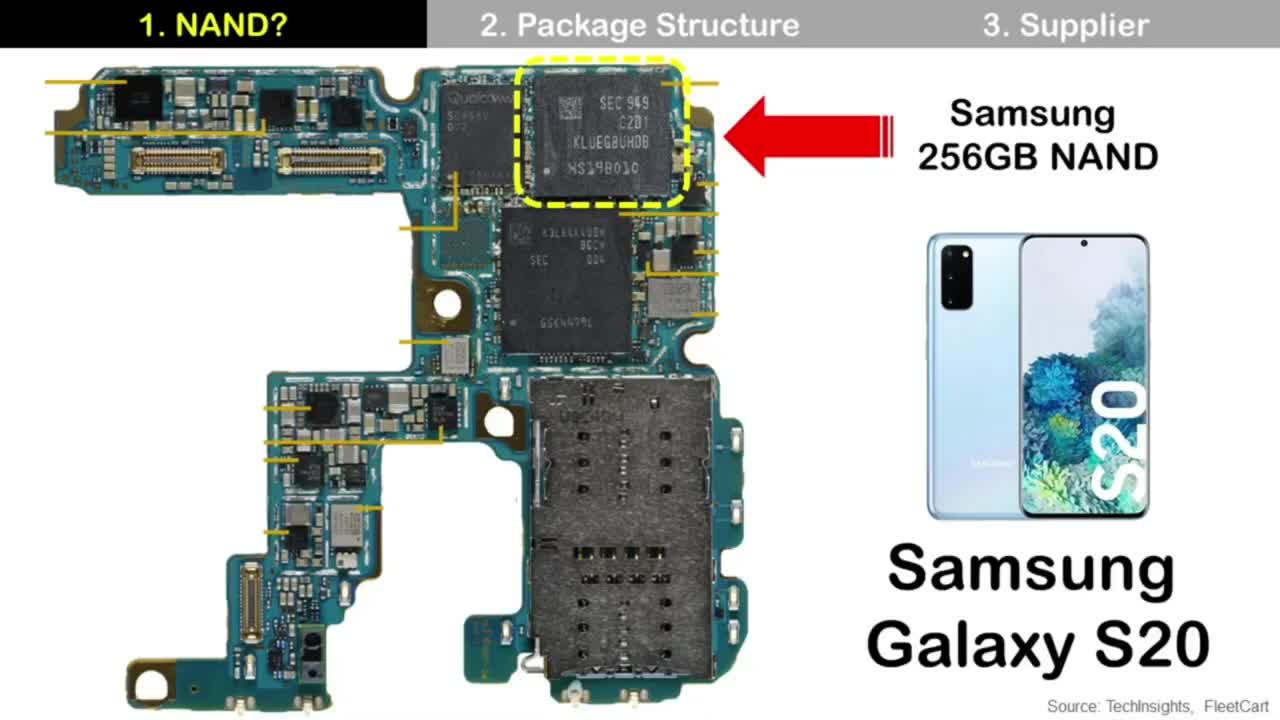

3178 隨著超高密度多芯片模組(Multiple Chip Module�,MCM)乃至系統(tǒng)級(jí)封裝(SiP)產(chǎn)品在5G、AI����、高性能運(yùn)算、汽車(chē)自動(dòng)駕駛等領(lǐng)域的普及�,2.5D 和 3D 晶圓級(jí)封裝技術(shù)備受設(shè)計(jì)人員青睞���。

2023-02-24 09:38:08 1723

1723 晶圓級(jí)芯片尺寸封裝-AN10439

2023-03-03 19:57:27 5

5 本應(yīng)用筆記討論ADI公司的晶圓級(jí)封裝(WLP),并提供WLP的PCB設(shè)計(jì)和SMT組裝指南����。

2023-03-08 19:23:00 4780

4780

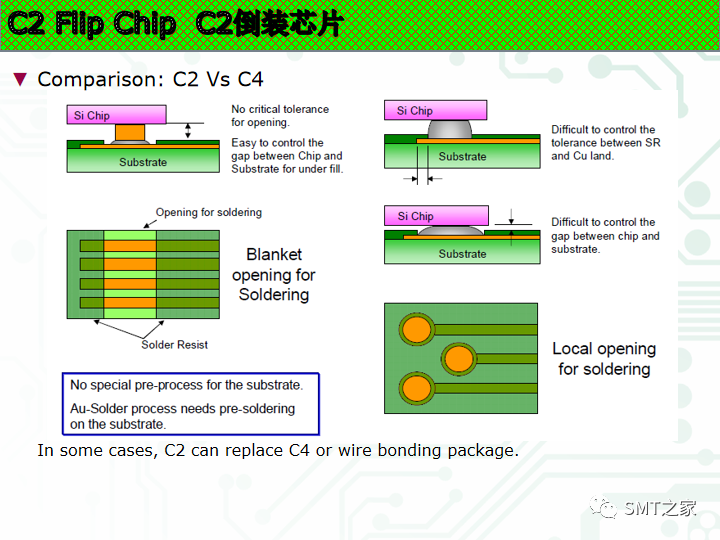

正在開(kāi)發(fā)新的凸點(diǎn)結(jié)構(gòu)以在倒裝芯片封裝中實(shí)現(xiàn)更高的互連密度,但它們復(fù)雜����、昂貴且越來(lái)越難以制造。

2023-05-22 09:46:51 2013

2013

半導(dǎo)體產(chǎn)品在由二維向三維發(fā)展��,從技術(shù)發(fā)展方向半導(dǎo)體產(chǎn)品出現(xiàn)了系統(tǒng)級(jí)封裝(SiP)等新的封裝方式��,從技術(shù)實(shí)現(xiàn)方法出現(xiàn)了倒裝(FlipChip)����,凸塊(Bumping)�����,晶圓級(jí)封裝(Wafer

2023-08-05 09:54:29 1021

1021

半導(dǎo)體產(chǎn)品在由二維向三維發(fā)展�����,從技術(shù)發(fā)展方向半導(dǎo)體產(chǎn)品出現(xiàn)了系統(tǒng)級(jí)封裝(SiP)等新的封裝方式,從技術(shù)實(shí)現(xiàn)方法出現(xiàn)了倒裝(FlipChip)���,凸塊(Bumping)��,晶圓級(jí)封裝

2023-08-14 09:59:24 1258

1258

晶圓封裝測(cè)試什么意思�? 晶圓封裝測(cè)試是指對(duì)半導(dǎo)體芯片(晶圓)進(jìn)行封裝組裝后�����,進(jìn)行電性能測(cè)試和可靠性測(cè)試的過(guò)程�。晶圓封裝測(cè)試是半導(dǎo)體芯片制造過(guò)程中非常重要的一步,它可以保證芯片質(zhì)量���,并確保生產(chǎn)出的芯片

2023-08-24 10:42:07 3376

3376 晶圓級(jí)封裝是在整個(gè)晶圓(wafer)的級(jí)別上進(jìn)行封裝��,而普通封裝是在單個(gè)芯片級(jí)別上進(jìn)行封裝��。晶圓級(jí)封裝通常在晶圓制造完成后�,將多個(gè)芯片同時(shí)封裝在同一個(gè)晶圓上����,形成多個(gè)封裝單元����。相比之下����,普通封裝將單個(gè)芯片分別封裝在獨(dú)立的封裝器件上。

2023-08-30 16:44:57 5859

5859 圓級(jí)封裝(WLP)技術(shù)的發(fā)展��。接下來(lái)討論了使用晶圓級(jí)封裝器件的實(shí)際方面��。討論的主題包括:確定給定器件的倒裝芯片/UCSP封裝的可用性����;通過(guò)其標(biāo)記識(shí)別倒裝芯片/UCSP;圓片級(jí)封裝件的可靠性���;尋找適用的可靠性信息�。

2023-10-16 15:02:47 2019

2019 晶圓級(jí)封裝是指晶圓切割前的工藝���。晶圓級(jí)封裝分為扇入型晶圓級(jí)芯片封裝(Fan-In WLCSP)和扇出型晶圓級(jí)芯片封裝(Fan-Out WLCSP),其特點(diǎn)是在整個(gè)封裝過(guò)程中���,晶圓始終保持完整���。

2023-10-18 09:31:05 4921

4921

扇出型晶圓級(jí)封裝技術(shù)的優(yōu)勢(shì)在于能夠利用高密度布線制造工藝�,形成功率損耗更低���、功能性更強(qiáng)的芯片封裝結(jié)構(gòu)�,讓系統(tǒng)級(jí)封裝(System in a Package, SiP)和3D芯片封裝更愿意采用扇出型晶圓級(jí)封裝工藝��。

2023-10-25 15:16:14 2051

2051

半導(dǎo)體產(chǎn)品在由二維向三維發(fā)展,從技術(shù)發(fā)展方向半導(dǎo)體產(chǎn)品出現(xiàn)了系統(tǒng)級(jí)封裝(SiP)等新的封裝方式����,從技術(shù)實(shí)現(xiàn)方法出現(xiàn)了倒裝(FlipChip),凸塊(Bumping)��,晶圓級(jí)封裝(Waferlevelpackage)�����,2.5D封裝(interposer�����,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)���。

2023-10-31 09:16:29 3859

3859

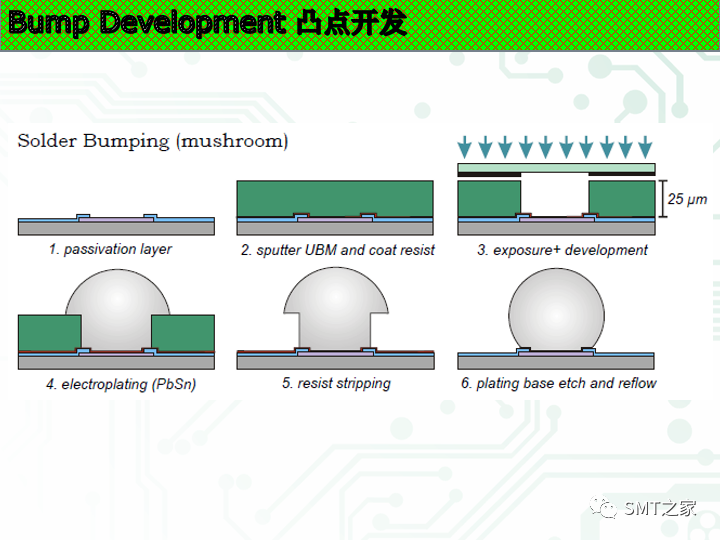

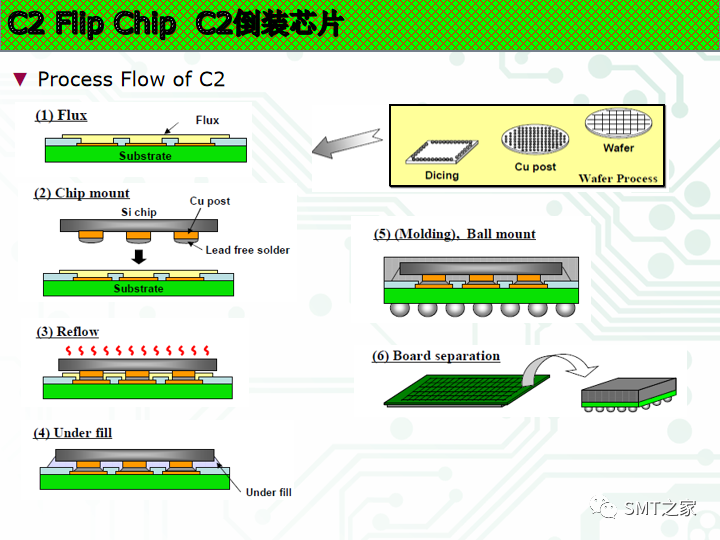

?詳細(xì)介紹了FC技術(shù)����,bumping技術(shù)�����,underfill技術(shù)和substrate技術(shù)����,以及倒裝封裝芯片的熱設(shè)計(jì),機(jī)械應(yīng)力等可靠性設(shè)計(jì)����。

2023-11-01 15:25:51 8

8 近年來(lái),隨著晶圓級(jí)封裝技術(shù)的不斷提升�,眾多芯片設(shè)計(jì)及封測(cè)公司開(kāi)始思考并嘗試采用晶圓級(jí)封裝技術(shù)替代傳統(tǒng)封裝。其中HRP(Heat Re-distribution Packaging)晶圓級(jí)先進(jìn)封裝工藝技術(shù)

2023-11-18 15:26:58 0

0 【科普】什么是晶圓級(jí)封裝

2023-12-07 11:34:01 2771

2771

傳統(tǒng)封裝需要將每個(gè)芯片都從晶圓中切割出來(lái)并放入模具中�����。晶圓級(jí)封裝 (WLP) 則是先進(jìn)封裝技術(shù)的一種 , 是指直接封裝仍在晶圓上的芯片�。

2024-01-12 09:29:13 6843

6843

共讀好書(shū) 半導(dǎo)體產(chǎn)品在由二維向三維發(fā)展,從技術(shù)發(fā)展方向半導(dǎo)體產(chǎn)品出現(xiàn)了系統(tǒng)級(jí)封裝(SiP)等新的封裝方式�,從技術(shù)實(shí)現(xiàn)方法出現(xiàn)了倒裝(FlipChip),凸塊(Bumping)�,晶圓級(jí)封裝(Wafer

2024-02-21 10:34:20 1565

1565

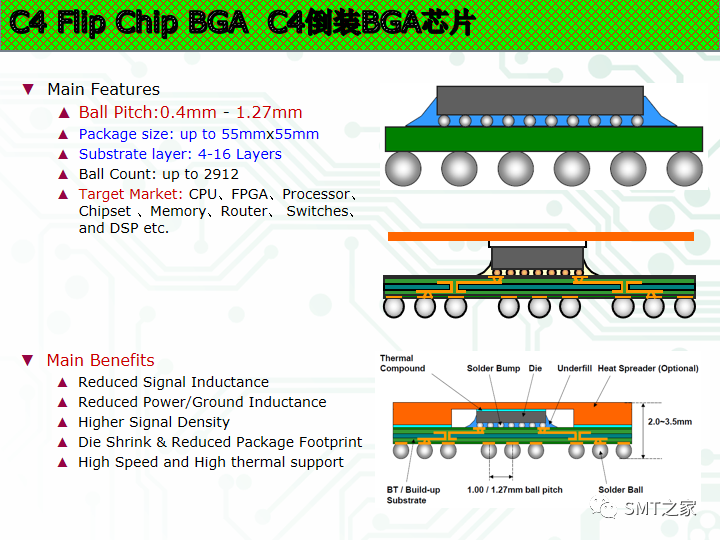

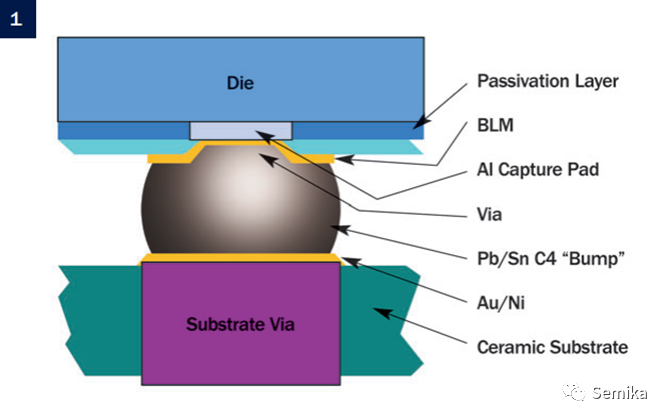

倒裝芯片技術(shù),也被稱為FC封裝技術(shù)���,是一種先進(jìn)的集成電路封裝技術(shù)���。在傳統(tǒng)封裝技術(shù)中,芯片被封裝在底部���,并通過(guò)金線連接到封裝基板上�。而倒裝芯片技術(shù)則將芯片直接翻轉(zhuǎn)并安裝在封裝基板上���,然后使用微小的焊點(diǎn)

2024-02-19 12:29:08 6594

6594

分為扇入型晶圓級(jí)芯片封裝(Fan-In WLCSP)和扇出型晶圓級(jí)芯片封裝(Fan-Out WLCSP)��,其特點(diǎn)是在整個(gè)封裝過(guò)程中�����,晶

2024-03-05 08:42:13 3555

3555

在半導(dǎo)體制造領(lǐng)域�,臺(tái)積電一直是技術(shù)革新的引領(lǐng)者。近日�,有知情人士透露,這家全球知名的芯片制造商正在積極探索一種全新的芯片封裝技術(shù)����,即從傳統(tǒng)的晶圓級(jí)封裝轉(zhuǎn)向面板級(jí)封裝,這將可能帶來(lái)封裝效率的顯著提升和成本的降低���。

2024-06-22 14:31:54 2310

2310 在本系列第七篇文章中�����,介紹了晶圓級(jí)封裝的基本流程���。本篇文章將側(cè)重介紹不同晶圓級(jí)封裝方法所涉及的各項(xiàng)工藝。晶圓級(jí)封裝可分為扇入型晶圓級(jí)芯片封裝(Fan-In WLCSP)�、扇出型晶圓級(jí)芯片封裝

2024-08-21 15:10:38 4450

4450

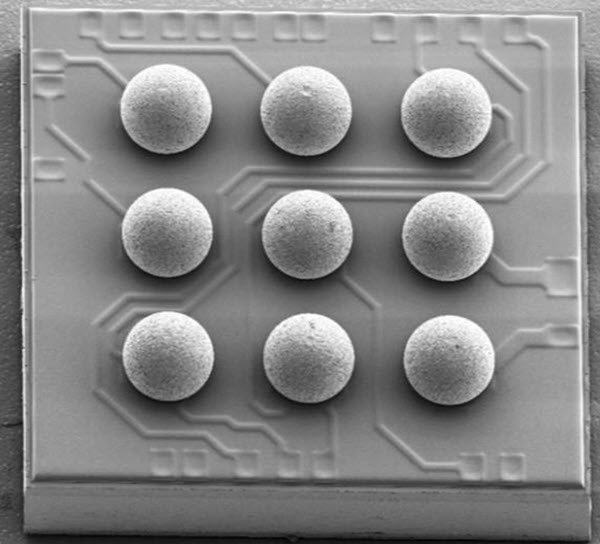

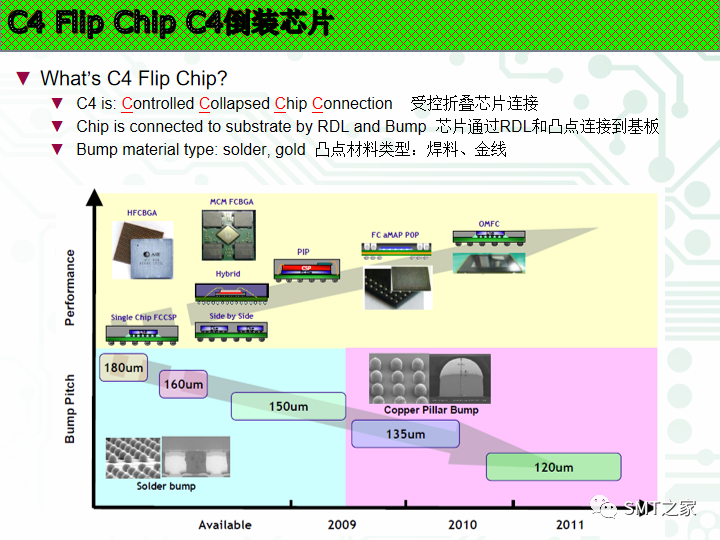

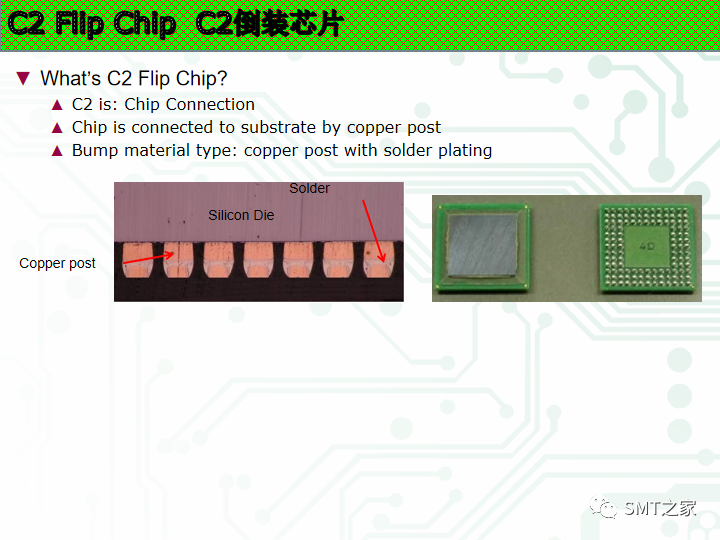

倒裝芯片是微電子電路先進(jìn)封裝的關(guān)鍵技術(shù)。它允許將裸芯片以面朝下的配置連接到封裝基板上�����,芯片和基板之間通過(guò)導(dǎo)電“凸起”進(jìn)行電氣連接�。

2024-10-18 15:17:19 2220

2220

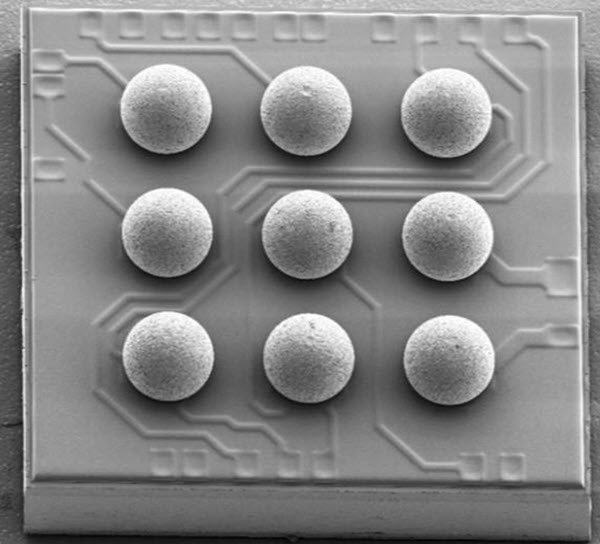

晶圓微凸點(diǎn)封裝�,更常見(jiàn)的表述是晶圓微凸點(diǎn)技術(shù)或晶圓級(jí)凸點(diǎn)技術(shù)(Wafer Bumping)��,是一種先進(jìn)的半導(dǎo)體封裝技術(shù)����。以下是對(duì)晶圓微凸點(diǎn)封裝的詳細(xì)解釋:

2024-12-11 13:21:23 1416

1416 ?? 一�、倒裝芯片概述 倒裝芯片(Flip Chip)���,又稱FC�,是一種先進(jìn)的半導(dǎo)體封裝技術(shù)����。該技術(shù)通過(guò)將芯片的有源面(即包含晶體管、電阻�����、電容等元件的一面)直接朝下�,與基板或載體上的焊盤(pán)進(jìn)行對(duì)齊

2024-12-21 14:35:38 3665

3665

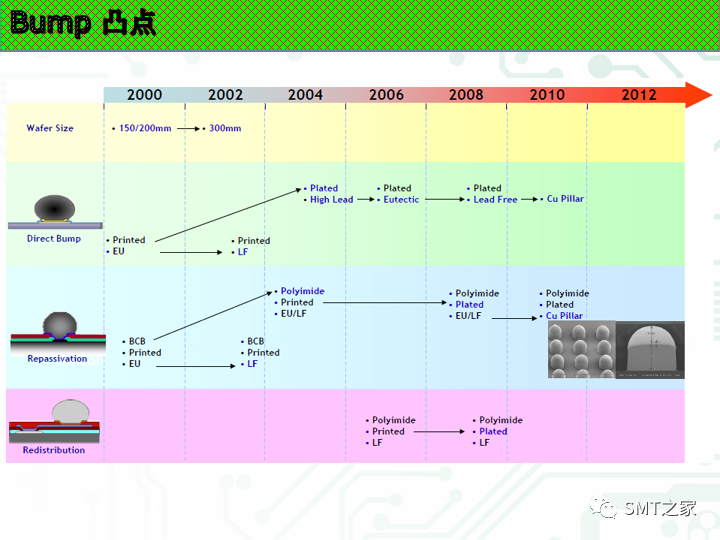

的“凸塊”或“凸球”。晶圓凸塊為倒裝芯片或板級(jí)半導(dǎo)體封裝的重要組成部分�����,已成為當(dāng)今消費(fèi)電子產(chǎn)品互連技術(shù)的標(biāo)準(zhǔn)��。凸塊在管芯和襯底之間提供比引線鍵合更短的路徑,以改善倒裝芯片封裝的電氣�、機(jī)械和熱性能。 倒裝芯片互連可減少信號(hào)傳播延遲��,提供更好的帶寬

2025-01-02 13:48:08 7708

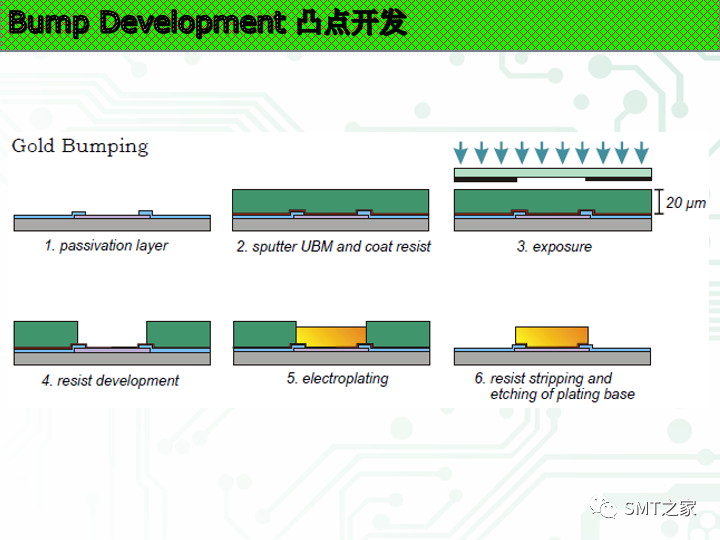

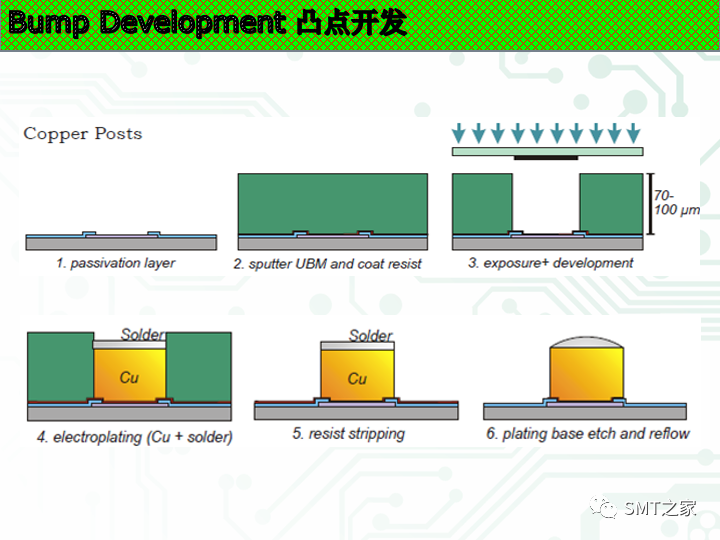

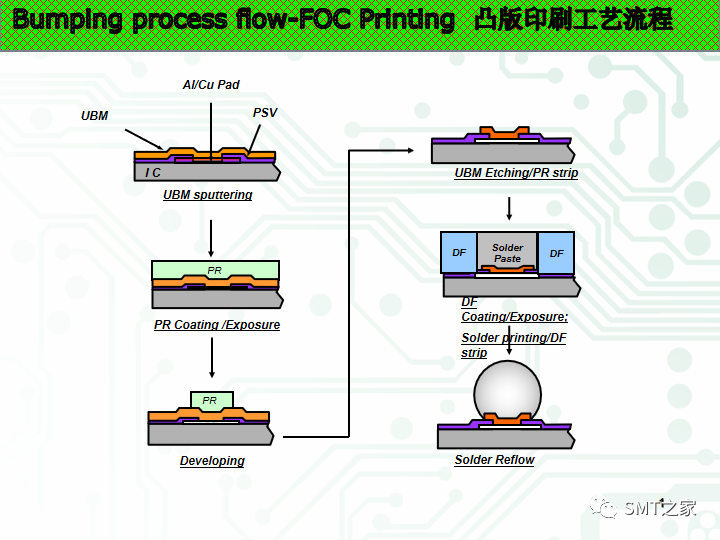

7708 隨著半導(dǎo)體技術(shù)的飛速發(fā)展����,晶圓級(jí)封裝(WLP)作為先進(jìn)封裝技術(shù)的重要組成部分,正逐漸成為集成電路封裝的主流趨勢(shì)�����。在晶圓級(jí)封裝過(guò)程中�����,Bump工藝扮演著至關(guān)重要的角色�����。Bump��,即凸塊�,是晶圓級(jí)封裝中

2025-03-04 10:52:57 4980

4980

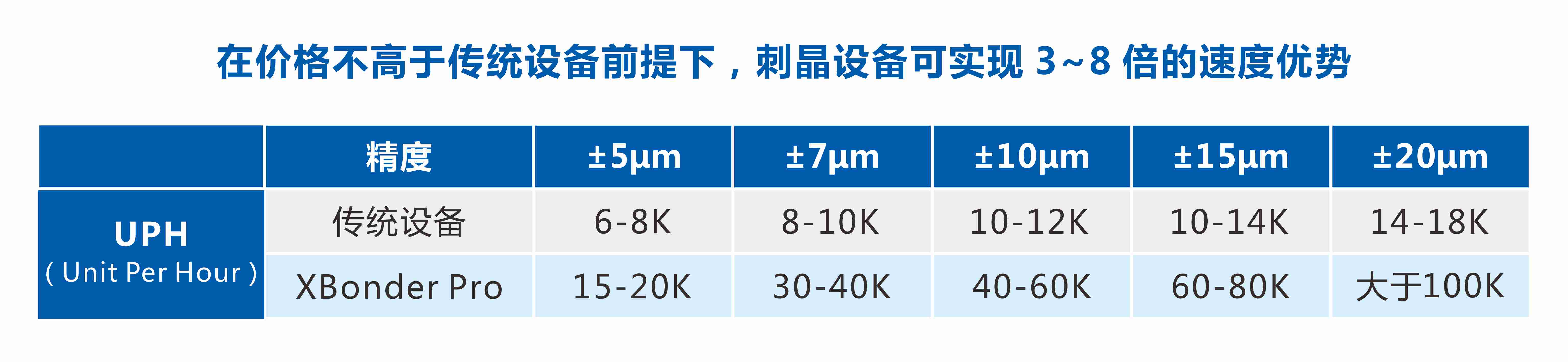

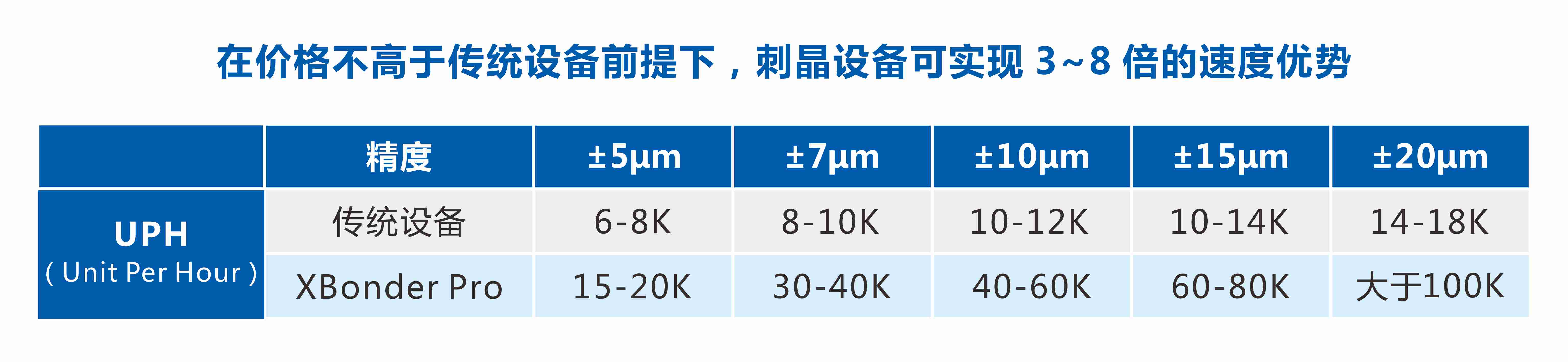

封裝領(lǐng)域的一次技術(shù)革命��。普萊信同時(shí)在和某全球最領(lǐng)先的封裝廠,某全球領(lǐng)先的功率器件公司就XBonder Pro在晶圓級(jí)封裝的應(yīng)用開(kāi)展合作���。 芯片的轉(zhuǎn)移是晶圓級(jí)封裝和板級(jí)封裝的核心工序��,由于高端的板級(jí)封裝和晶圓級(jí)封裝需要在貼片完成后��,進(jìn)行RDL等工藝,

2025-03-04 11:28:05 1186

1186

圓片級(jí)封裝(WLP)���,也稱為晶圓級(jí)封裝��,是一種直接在晶圓上完成大部分或全部封裝測(cè)試程序�,再進(jìn)行切割制成單顆組件的先進(jìn)封裝技術(shù) ����。WLP自2000年左右問(wèn)世以來(lái),已逐漸成為半導(dǎo)體封裝領(lǐng)域的主流技術(shù)�,深刻改變了傳統(tǒng)封裝的流程與模式。

2025-05-08 15:09:36 2068

2068

在微電子行業(yè)飛速發(fā)展的背景下����,封裝技術(shù)已成為連接芯片創(chuàng)新與系統(tǒng)應(yīng)用的核心紐帶。其核心價(jià)值不僅體現(xiàn)于物理防護(hù)與電氣/光學(xué)互聯(lián)等基礎(chǔ)功能�,更在于應(yīng)對(duì)多元化市場(chǎng)需求的適應(yīng)性突破�����,本文著力介紹晶圓級(jí)扇入封裝��,分述如下�。

2025-06-03 18:22:20 1055

1055

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論