IDT公司的9ZXL1951D是19路輸出零延遲時(shí)鐘驅(qū)動(dòng)器,具有用于PCIe和CPU的第二代增強(qiáng)性能緩沖器,滿足所有發(fā)表過的QPI/UPI, DB2000Q和PCIe Gen1–5抖動(dòng)指標(biāo).器件的ZDB模式相位抖動(dòng)器:

PCIe Gen5 CC < 24fs RMS (低帶寬),QPI/UPI 11.4GB/s < 110fs RMS (低帶寬),IF-UPI附加抖動(dòng)< 130fs RMS (低帶寬);而Fanout緩沖器模式附加相抖動(dòng)器: PCIe Gen5 CC < 15fs RMS,DB2000Q 附加抖動(dòng) < 25fs RMS,QPI/UPI 11.4GB/s < 40fs RMS,IF-UPI 附加抖動(dòng) < 70fs RMS,周期到周期的抖動(dòng)<50ps,輸出到輸出偏差<50ps. LP-HCSL輸出,

每個(gè)輸出對(duì)可省略多達(dá)4個(gè)電阻,9個(gè)可選擇SMBus地址.工作溫度-40℃ 到 +85℃ .主要用在服務(wù)器,nVME存儲(chǔ),網(wǎng)絡(luò),加速度計(jì)和工業(yè)應(yīng)用.本文介紹了9ZXL1951D主要指標(biāo)和優(yōu)勢(shì),框圖, 負(fù)載相位抖動(dòng)測(cè)量圖,以及PCIe時(shí)鐘發(fā)生器評(píng)估板EVK9ZXL1951D主要特性和電路圖.

The 9ZXL15x0D/9ZXL19x0D/9ZXL1951D devices comprise a family of 2nd-generation enhanced performance buffers for PCIe and CPU applications. The family meets all published QPI/UPI, DB2000Q and PCIe Gen1–5 jitter specifications. Devices are either 15 or 19 outputs. The devices function as both fanout (FOB) and zero-delay (ZDB) buffers. All devices meet DB2000Q and DB1900Z jitter and skew requirements.

9ZXL1951D主要指標(biāo):

? ZDB Mode phase jitter:

? PCIe Gen5 CC < 24fs RMS (Low Bandwidth)

? QPI/UPI 11.4GB/s < 110fs RMS (Low Bandwidth)

? IF-UPI additive jitter < 130fs RMS (Low Bandwidth)

? Fanout Buffer Mode additive phase jitter:

? PCIe Gen5 CC < 15fs RMS

? DB2000Q additive jitter < 25fs RMS

? QPI/UPI 11.4GB/s < 40fs RMS

? IF-UPI additive jitter < 70fs RMS

? Cycle-to-cycle jitter: < 50ps

? Output-to-output skew: < 50ps

9ZXL1951D主要特性:

? LP-HCSL outputs eliminate up to 4 resistors per output pair

? 9 selectable SMBus addresses

? Selectable PLL bandwidths minimizes jitter peaking in cascaded PLL topologies

? Hardware/SMBus control of ZDB and FOB modes allow change without power cycle

? 8 OE# pins support PCIe CLKREQ# functionality (9ZXL1951)

? Spread spectrum compatible

? 100MHz and 133.33MHz ZDB mode (9ZXL15x0, 9ZXL19x0)

? 100MHz ZDB mode (9ZXL1951)

? 1–400MHz FOB mode (all devices)

? -40°C to +85°C operating temperature range

? Package information: see Ordering Information table

輸出:

? 15 or 19 Low-power HCSL (LP-HCSL) output pairs

PCIe時(shí)鐘架構(gòu):

? Common Clocked (CC)

? Independent Reference (IR) with and without spread spectrum

9ZXL1951D典型應(yīng)用:

? Servers

? nVME Storage

? Networking

? Accelerators

? Industrial

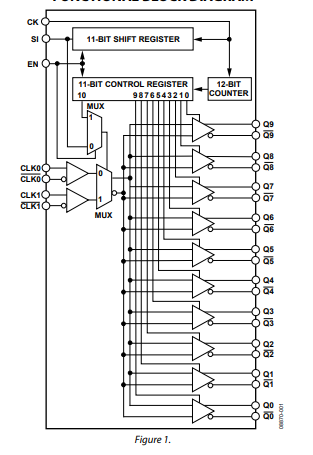

圖1. 9ZXL1951D框圖

圖2. 采用相位噪音分析儀測(cè)量負(fù)載相位抖動(dòng)圖

圖3. 采用示波器測(cè)量負(fù)載相位抖動(dòng)圖

PCIe時(shí)鐘發(fā)生器評(píng)估板EVK9ZXL1951D

The evaluation board is designed to help the customer evaluate the 9ZXL1951D. The device is programmable through an SMBus interface. This user guide details the board set and connection, as well as the companion GUI installation for communicating to the device. The board has a self-contained USB to SMBus interface.

圖4. 評(píng)估板EVK9ZXL1951D外形圖

圖5. 評(píng)估板EVK9ZXL1951D電路圖: 9ZXL1951D連接

圖6. 評(píng)估板EVK9ZXL1951D電路圖: USB接口和電源

編輯:jq

-

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

54文章

9016瀏覽量

153371 -

cpu

+關(guān)注

關(guān)注

68文章

11218瀏覽量

222959 -

PCIe

+關(guān)注

關(guān)注

16文章

1422瀏覽量

87551

發(fā)布評(píng)論請(qǐng)先 登錄

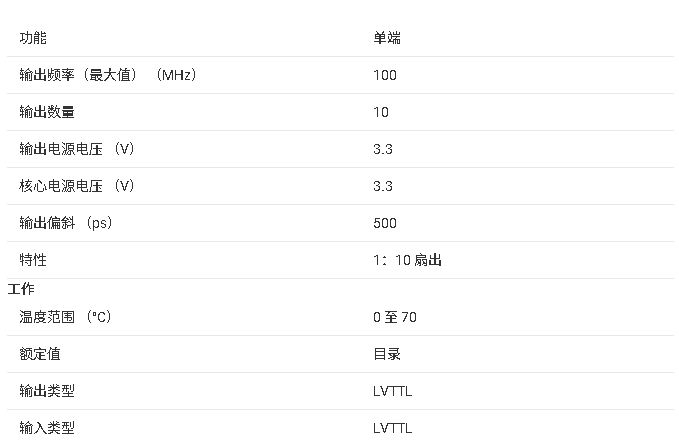

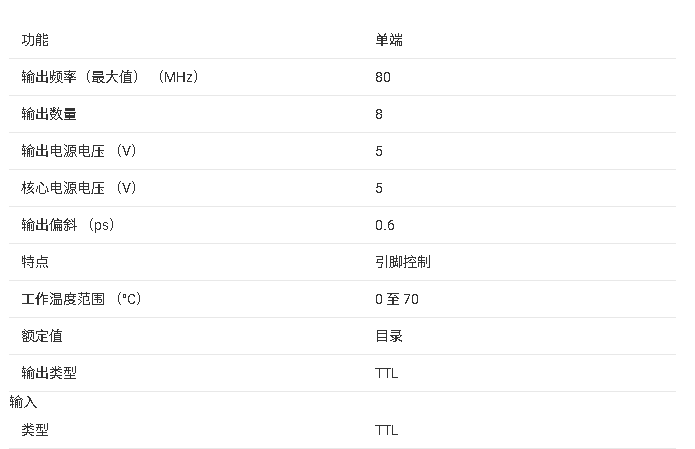

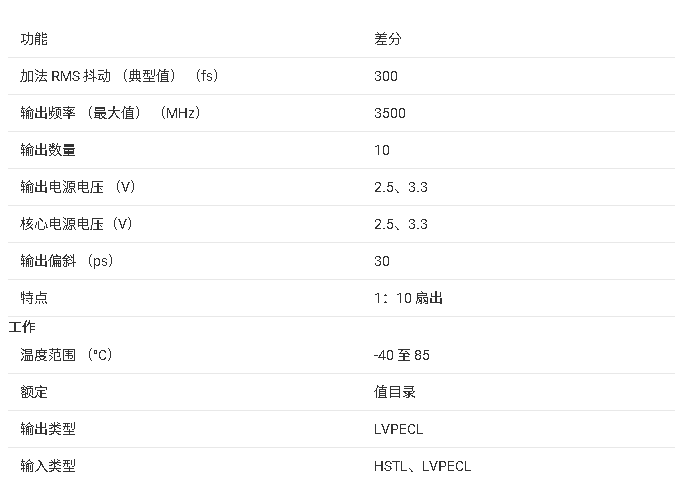

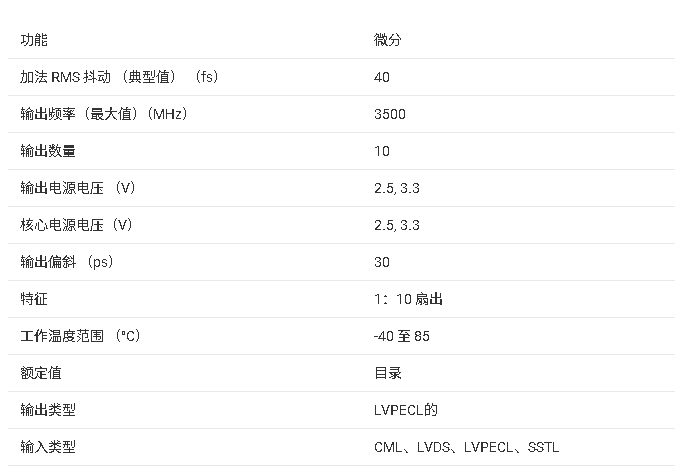

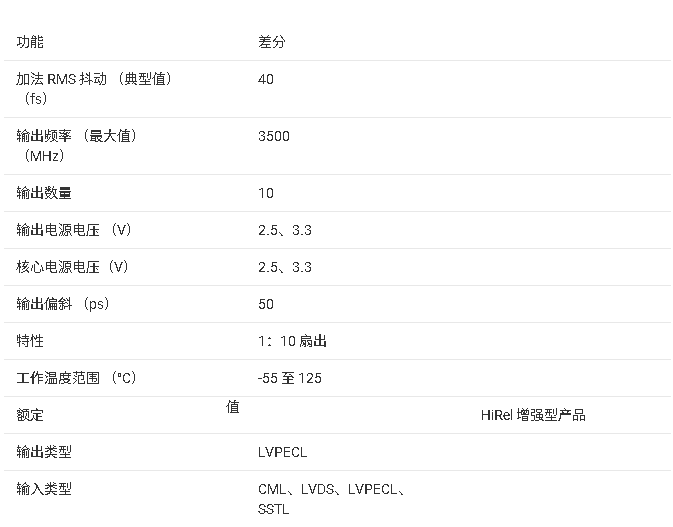

?CDC2351 1線轉(zhuǎn)10線時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

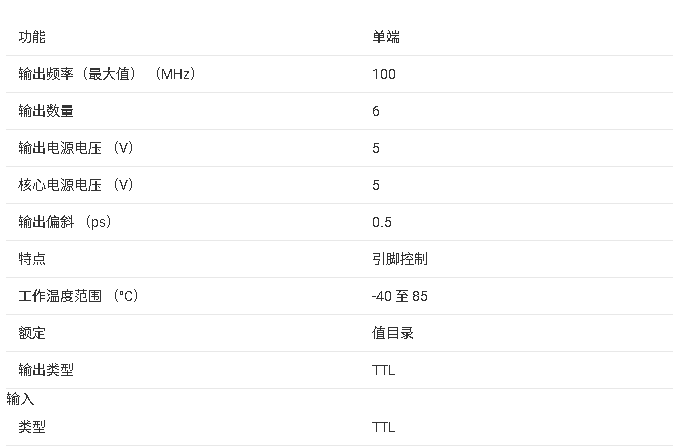

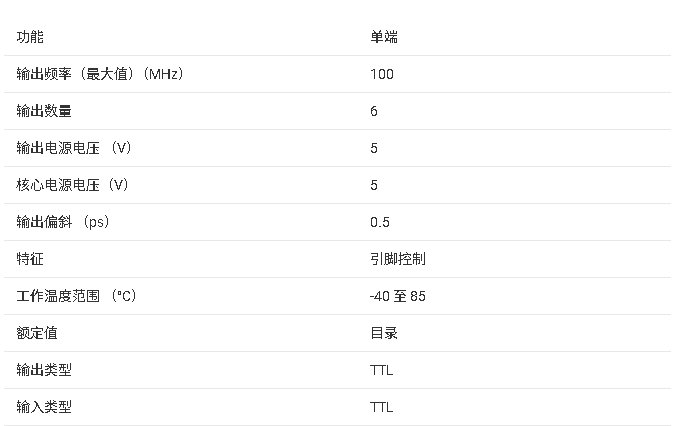

?CDC391 時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

?CDC329A 時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

?CDC328A 時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

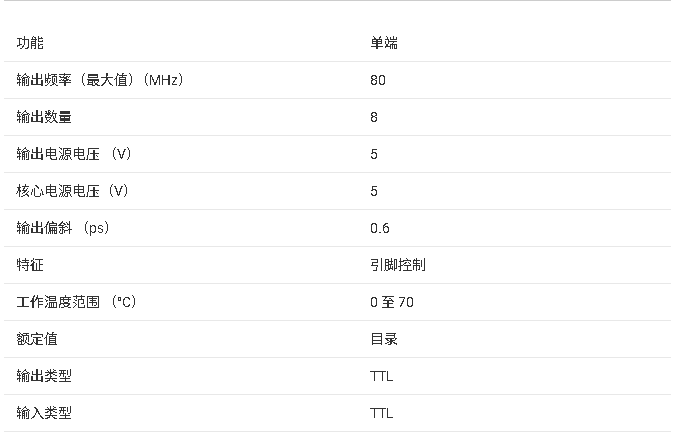

?CDC340 1線至8線時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

?CDC341 1線至8線時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

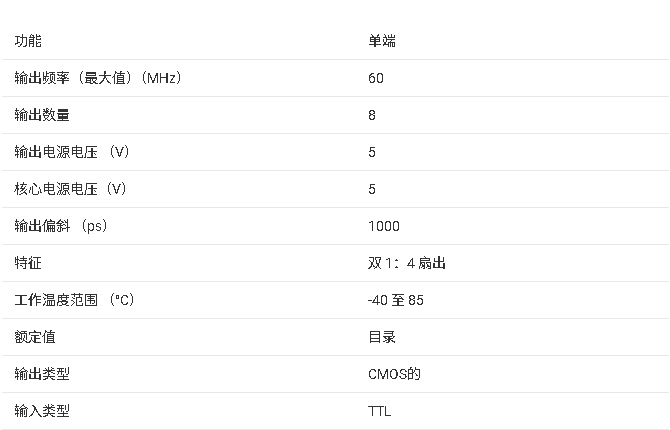

?CDC208 雙路1線至4線時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

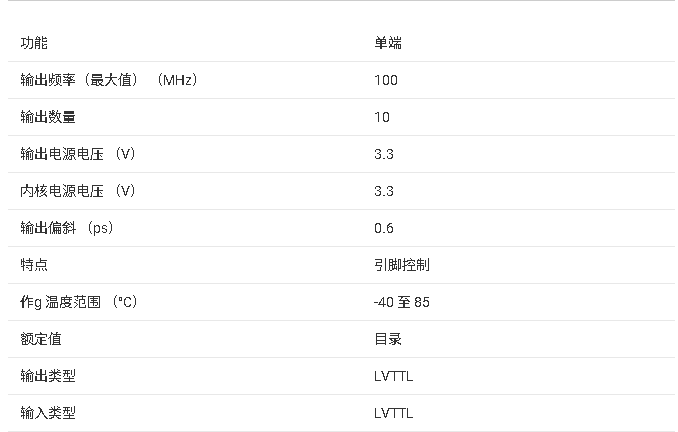

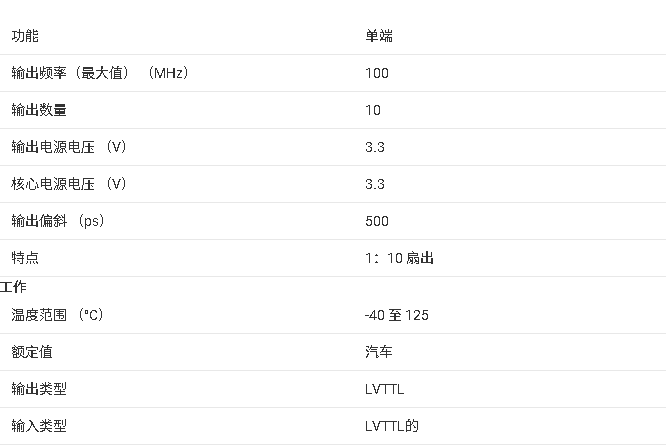

?CDC351 1:10時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

?CDC2351-Q1 1:10時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

?CDCVF25081 3.3-V 鎖相環(huán)時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

?CDCLVP110 1:10 LVPECL/HSTL時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

?CDCLVP215 低電壓雙差分1:5 LVPECL時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

?CDCLVP111 低電壓1:10 LVPECL時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

?CDCLVP111-EP 低電壓1:10 LVPECL時(shí)鐘驅(qū)動(dòng)器技術(shù)文檔總結(jié)

ADN4670可編程低壓1:10 LVDS時(shí)鐘驅(qū)動(dòng)器技術(shù)手冊(cè)

剖析IDT 9ZXL1951D 19路輸出零延遲時(shí)鐘驅(qū)動(dòng)器方案

剖析IDT 9ZXL1951D 19路輸出零延遲時(shí)鐘驅(qū)動(dòng)器方案

評(píng)論