Zynq上的非對(duì)稱(chēng)多核處理器

Zynq SoC 還擁有大量共享資源,常見(jiàn)示例包括 I/O 外設(shè)、片上存儲(chǔ)器、中斷控制器分配器、L2....

SystemVerilog包的簡(jiǎn)介與使用

最初的Verilog語(yǔ)言沒(méi)有一個(gè)可用于多個(gè)模塊的定義。每個(gè)模塊都必須有任務(wù)、函數(shù)、常量和其他共享定義....

Vitis HLS的基礎(chǔ)知識(shí)科普

VitisHLS是一種高層次綜合工具,支持將C、C++和OpenCL函數(shù)硬連線到器件邏輯互連結(jié)構(gòu)和R....

介紹幾個(gè)關(guān)于ISP算法架構(gòu)的項(xiàng)目

用python實(shí)現(xiàn)的ISP架構(gòu),整體項(xiàng)目架構(gòu)不如OpenISP,但是有幾個(gè)算法是OpenISP沒(méi)有的....

匠人精神是怎么用在FPGA存儲(chǔ)器

FPGA之所以有這樣的能力,是由它本身的結(jié)構(gòu)決定的。比如FPGA有著很強(qiáng)的硬件并行性,能像GPU那樣....

SystemVerilog為工程師定義新的數(shù)據(jù)類(lèi)型提供了一種機(jī)制

為了使源代碼更易于閱讀和維護(hù),typedef名稱(chēng)應(yīng)該使用一種命名約定,使名稱(chēng)明顯代表用戶自定義類(lèi)型。....

通過(guò)無(wú)線wifi下載調(diào)試fpga的一種方法

上邊是整個(gè)框圖,主要的數(shù)據(jù)流是Vivado通過(guò)PC上的WIFI鏈接到WIFI路由器上,然后對(duì)同一個(gè)局....

幾個(gè)視頻/圖像處理的項(xiàng)目分享

F-I-L是一個(gè)FPGA平臺(tái)的開(kāi)源的圖像處理庫(kù),已經(jīng)擁有了許多常用操作,并在不斷更新中。這些操作被以....

使用Xilinx Vivado創(chuàng)建自己板卡文件

board.xml - 定義關(guān)于板的所有信息。它包括基本信息(例如電路板名稱(chēng)、描述、供應(yīng)商)、有關(guān)板....

介紹幾個(gè)脈沖神經(jīng)網(wǎng)絡(luò)的開(kāi)源項(xiàng)目

ODIN 是一種在線學(xué)習(xí)數(shù)字脈沖神經(jīng)處理器,在 2019 年發(fā)表在IEEE Transactions....

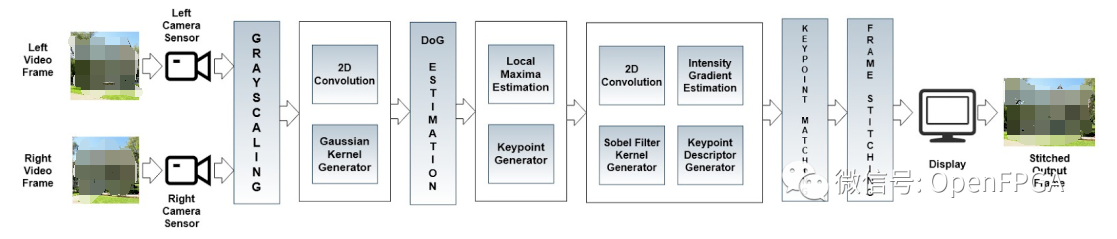

基于FPGA的視頻圖像拼接融合

視頻流的每個(gè)單獨(dú)幀將具有對(duì)應(yīng)于紅色、綠色和藍(lán)色的三個(gè)通道。視頻幀中的顏色信息不會(huì)增強(qiáng)特征檢測(cè)。此外,....

網(wǎng)絡(luò)和變量的未壓縮數(shù)組

數(shù)組的維度定義了數(shù)組可以存儲(chǔ)的元素總數(shù)。未壓縮的數(shù)組可以用任意數(shù)量的維度聲明,每個(gè)維度存儲(chǔ)指定數(shù)量的....

DMA控制器介紹及示例演示詳解

我們上一節(jié)談到使用 DMA(直接內(nèi)存訪問(wèn))的好處已經(jīng)變得顯而易見(jiàn)。到了這一步,我們留下了人類(lèi)長(zhǎng)期以來(lái)....

Verilog/FPGA開(kāi)源項(xiàng)目卷積神經(jīng)網(wǎng)絡(luò)

CNN 是多層感知器的正則化版本。多層感知器通常表示全連接網(wǎng)絡(luò),即一層中的每個(gè)神經(jīng)元都連接到下一層中....

離散端口的語(yǔ)法和使用指南

SystemVerilog提供用于聲明端口列表和端口聲明的編碼樣式:組合樣式、傳統(tǒng)樣式和具有組合類(lèi)型....

ZYNQ:使用PL將任務(wù)從PS加載到PL端

ARM 的 AXI 是一種面向突發(fā)的協(xié)議,旨在提供高帶寬同時(shí)提供低延遲。每個(gè) AXI 端口都包含獨(dú)立....

數(shù)字硬件建模SystemVerilog-網(wǎng)絡(luò)

每個(gè)SystemVerilog網(wǎng)絡(luò)類(lèi)型都有特定的語(yǔ)義規(guī)則,這些規(guī)則會(huì)影響多個(gè)驅(qū)動(dòng)程序的解析方式。雖然....

RTL級(jí)的基本要素和設(shè)計(jì)步驟

頂層設(shè)計(jì):RTL設(shè)計(jì)推薦使用自頂而下的設(shè)計(jì)方法,因?yàn)檫@種設(shè)計(jì)方法與模塊規(guī)劃的順序一致,而且更有利于進(jìn)....

SystemVerilog常用可綜合IP模塊庫(kù)

了解決這個(gè)復(fù)雜的問(wèn)題,設(shè)計(jì)了這個(gè)庫(kù),它可以幫助您簡(jiǎn)化設(shè)計(jì)流程。使用一些簡(jiǎn)單的 API 可以輕松地在測(cè)....

了解Zynq SoC的私有看門(mén)狗定時(shí)器

每個(gè)A9處理器都有私有的32位定時(shí)器和32位看門(mén)狗定時(shí)器。兩個(gè)處理器共享一個(gè)64位定時(shí)器。這些定時(shí)器....

從算法到RTL實(shí)現(xiàn)的問(wèn)題

我們首先要根據(jù)實(shí)際需求,針對(duì)某方面的信號(hào)處理問(wèn)題,做一個(gè)鏈路級(jí)或模塊級(jí)快速仿真驗(yàn)證設(shè)計(jì)。最常見(jiàn)的比如....

什么是張量處理單元(TPU)

該項(xiàng)目的目的是創(chuàng)建一個(gè)與谷歌的張量處理單元具有相似架構(gòu)的機(jī)器學(xué)習(xí)協(xié)處理器。該實(shí)現(xiàn)的資源可定制,可以以....

TPU的系統(tǒng)架構(gòu)

通常,ASIC 帶來(lái)的麻煩多于其價(jià)值。他們需要很長(zhǎng)時(shí)間來(lái)設(shè)計(jì):Google 花了15 個(gè)月的時(shí)間來(lái)開(kāi)....

“軟核”硬做-ODrive(FPGA版本)

核心CPU是XX32FXXX,在工業(yè)控制領(lǐng)域其實(shí)FPGA占比也很大,所以能不能用FPGA做一個(gè)ODr....

FPGA/IC領(lǐng)域術(shù)語(yǔ)表

Amdahl's Law: Amdahl's law of diminishin....

System Verilog-文本值

文本整數(shù)值是一個(gè)整數(shù),沒(méi)有小數(shù)點(diǎn)。(IEEE 1800 SystemVerilog標(biāo)準(zhǔn)使用術(shù)語(yǔ)“整數(shù)....

Perl語(yǔ)言在代碼自動(dòng)生成中的應(yīng)用實(shí)例

Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL語(yǔ)言?xún)H是對(duì)已知硬....

FIR數(shù)字濾波器設(shè)計(jì)

數(shù)字濾波器的輸入輸出均為數(shù)字信號(hào),信號(hào)通過(guò)數(shù)字濾波器后,可以改變頻率成分的相對(duì)比例或?yàn)V除某些頻率成分....

Zynq SoC 設(shè)備上的多種用途

這篇博文特別關(guān)注 Zynq SoC 的多用途 IO (MIO, Multipurpose IO) 模....

SystemVerilog對(duì)硬件功能如何進(jìn)行建模

本文定義了通常用于描述使用SystemVerilog對(duì)硬件功能進(jìn)行建模的詳細(xì)級(jí)別的術(shù)語(yǔ)。