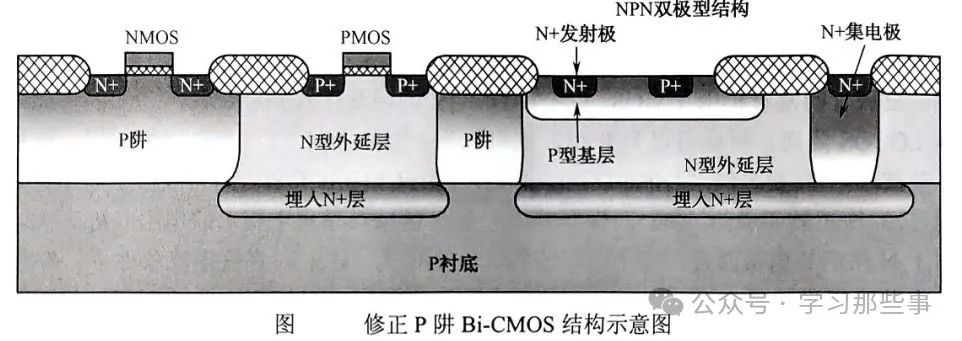

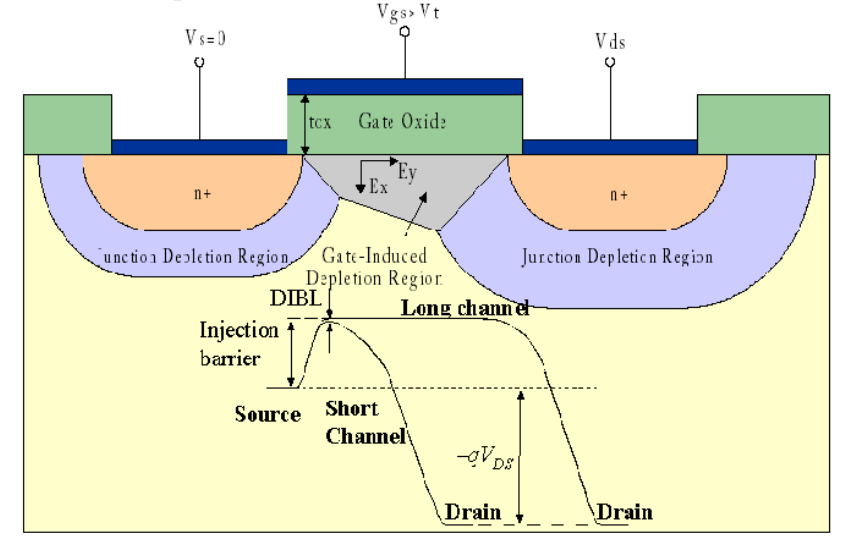

FinFET技術(shù)在晶圓制造中的優(yōu)勢(shì)

本文通過(guò)介紹傳統(tǒng)平面晶體管的局限性,從而引入FinFET技術(shù)的原理、工藝和優(yōu)勢(shì)。

可靠性測(cè)試結(jié)構(gòu)設(shè)計(jì)概述

深入理解設(shè)計(jì)規(guī)則,設(shè)計(jì)者可在可靠性測(cè)試結(jié)構(gòu)優(yōu)化中兼顧性能、成本與質(zhì)量,推動(dòng)半導(dǎo)體技術(shù)的持續(xù)創(chuàng)新。

芯片制造中的互連工藝介紹

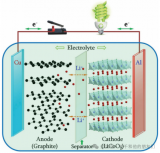

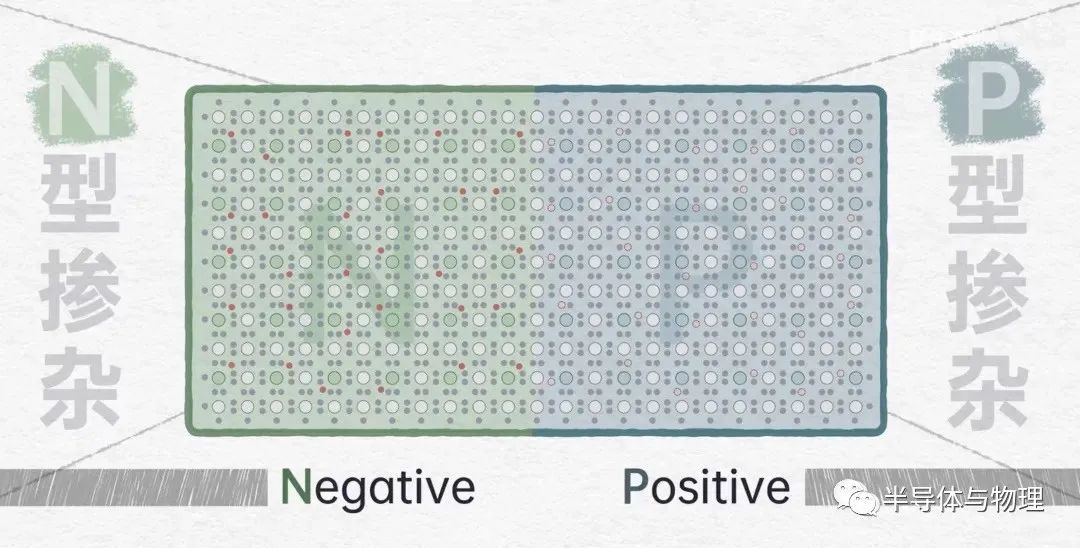

半導(dǎo)體是一種介于導(dǎo)體和絕緣體之間的導(dǎo)電性,半導(dǎo)體通過(guò)參雜可以使得能夠精確地控制電流的流動(dòng)。通過(guò)基于晶....

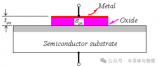

芯片制造中的二氧化硅介紹

二氧化硅是芯片制造中最基礎(chǔ)且關(guān)鍵的絕緣材料。本文介紹其常見(jiàn)沉積方法與應(yīng)用場(chǎng)景,解析SiO?在柵極氧化....

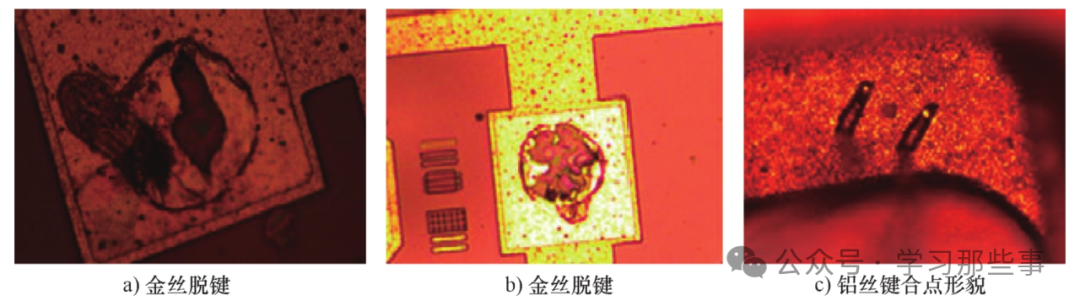

引線鍵合里常見(jiàn)的金鋁鍵合問(wèn)題

金鋁效應(yīng)是集成電路封裝中常見(jiàn)的失效問(wèn)題,嚴(yán)重影響器件的可靠性。本文系統(tǒng)解析其成因、表現(xiàn)與演化機(jī)制,并....

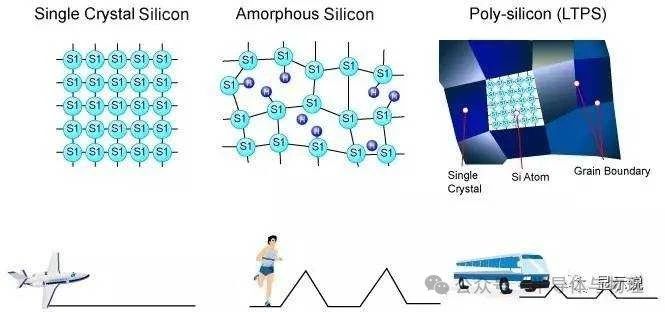

LPCVD方法在多晶硅制備中的優(yōu)勢(shì)與挑戰(zhàn)

本文圍繞單晶硅、多晶硅與非晶硅三種形態(tài)的結(jié)構(gòu)特征、沉積技術(shù)及其工藝參數(shù)展開(kāi)介紹,重點(diǎn)解析LPCVD方....

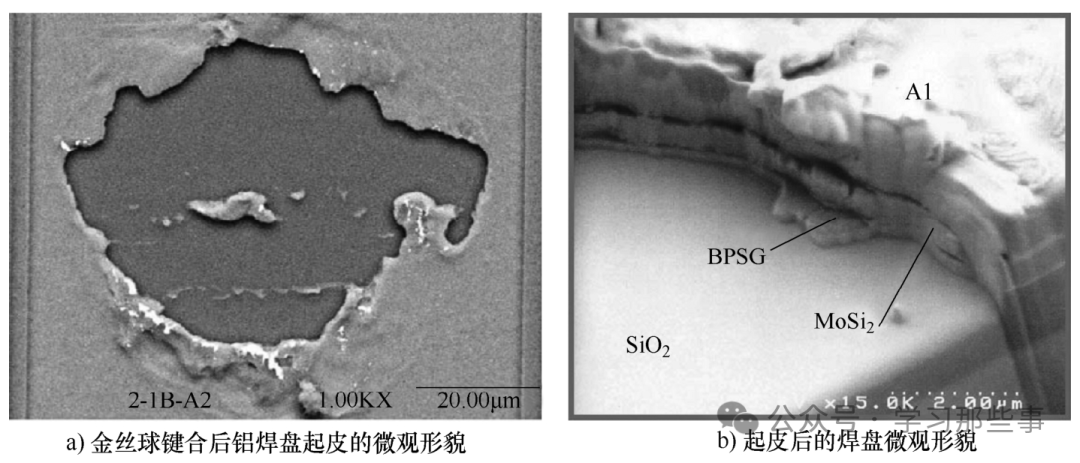

芯片焊盤(pán)起皮的成因解析

本文深入解析了焊盤(pán)起皮的成因、機(jī)制及其與工藝參數(shù)之間的關(guān)系,結(jié)合微觀形貌圖和仿真分析,系統(tǒng)探討了劈刀....

激光粉末涂層固化的優(yōu)勢(shì)和工作原理

激光固化技術(shù)采用紅外激光器,首先使靜電噴涂在零件表面的粉末涂料顆??焖倌z化,隨后完成最終固化。熔化....

鉛酸電池面臨的技術(shù)挑戰(zhàn)

當(dāng)加斯頓·普朗特在160多年前發(fā)明鉛酸電池時(shí),他可能未曾預(yù)料到這一發(fā)明將催生一個(gè)價(jià)值數(shù)十億美元的產(chǎn)業(yè)....

如何制定芯片封裝方案

封裝方案制定是集成電路(IC)封裝設(shè)計(jì)中的關(guān)鍵環(huán)節(jié),涉及從芯片設(shè)計(jì)需求出發(fā),制定出滿足功能、電氣性能....

印刷電路板的結(jié)構(gòu)和類型及組裝工藝步驟

經(jīng)過(guò)封裝與測(cè)試的芯片,理論上已具備使用條件。然而在現(xiàn)實(shí)生活里,一個(gè)集成電路產(chǎn)品通常需要眾多芯片共同組....

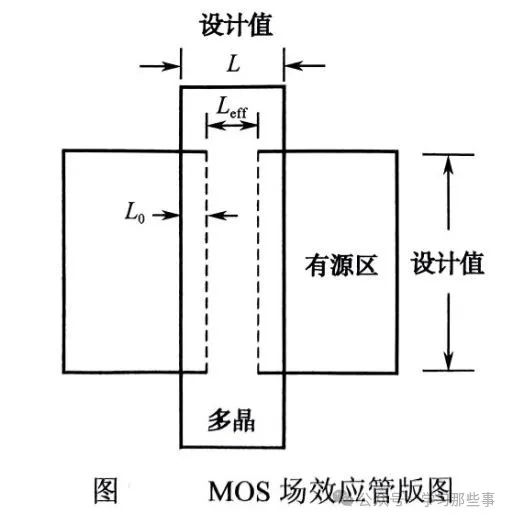

集成電路版圖設(shè)計(jì)的基本概念和關(guān)鍵步驟

在集成電路設(shè)計(jì)中,版圖(Layout)是芯片設(shè)計(jì)的核心之一,通常是指芯片電路的物理實(shí)現(xiàn)圖。它描述了電....

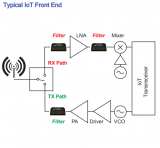

混合信號(hào)設(shè)計(jì)的概念、挑戰(zhàn)與發(fā)展趨勢(shì)

本文介紹了集成電路設(shè)計(jì)領(lǐng)域中混合信號(hào)設(shè)計(jì)的概念、挑戰(zhàn)與發(fā)展趨勢(shì)。

光刻工藝的主要流程和關(guān)鍵指標(biāo)

光刻工藝貫穿整個(gè)芯片制造流程的多次重復(fù)轉(zhuǎn)印環(huán)節(jié),對(duì)于集成電路的微縮化和高性能起著決定性作用。隨著半導(dǎo)....

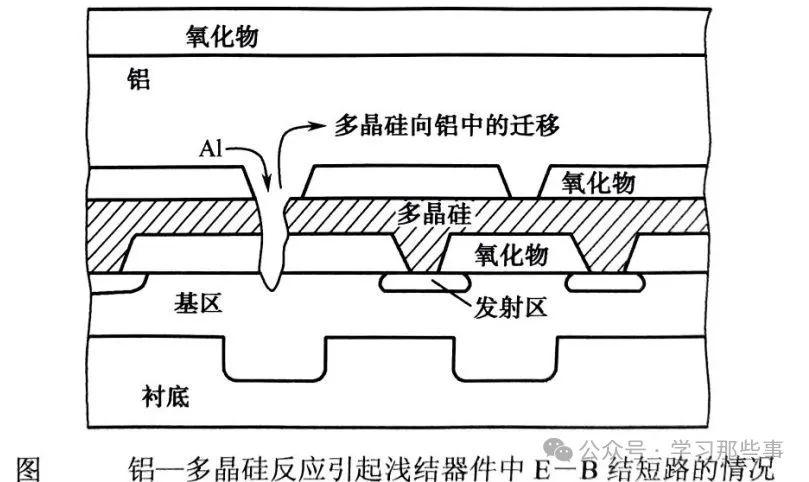

詳解半導(dǎo)體集成電路的失效機(jī)理

半導(dǎo)體集成電路失效機(jī)理中除了與封裝有關(guān)的失效機(jī)理以外,還有與應(yīng)用有關(guān)的失效機(jī)理。

單晶硅納米力學(xué)性能測(cè)試方法

在材料納米力學(xué)性能測(cè)試的眾多方法中,納米壓痕技術(shù)憑借其獨(dú)特的優(yōu)勢(shì)脫穎而出,成為當(dāng)前的主流測(cè)試手段。