什么是晶圓級(jí)扇入封裝技術(shù)

在微電子行業(yè)飛速發(fā)展的背景下,封裝技術(shù)已成為連接芯片創(chuàng)新與系統(tǒng)應(yīng)用的核心紐帶。其核心價(jià)值不僅體現(xiàn)于物....

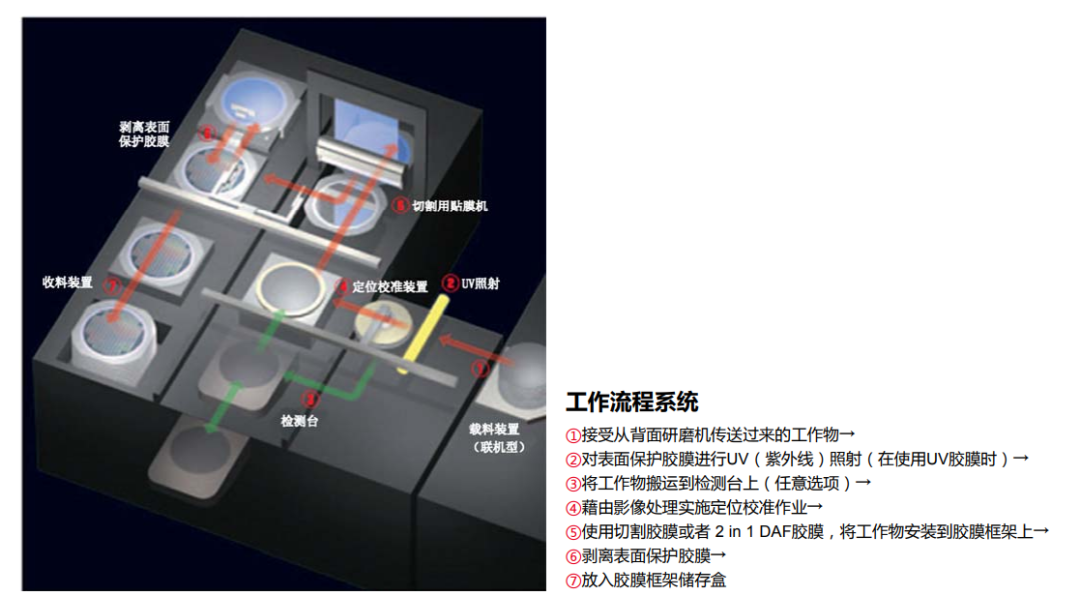

晶圓減薄工藝分為哪幾步

“減薄”,也叫 Back Grinding(BG),是將晶圓(Wafer)背面研磨至目標(biāo)厚度的工藝步....

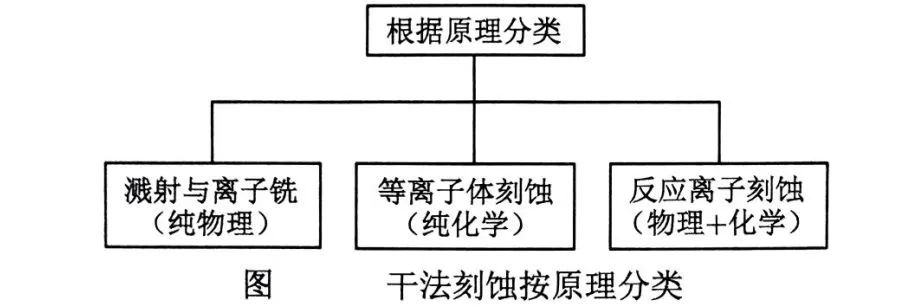

一文詳解干法刻蝕工藝

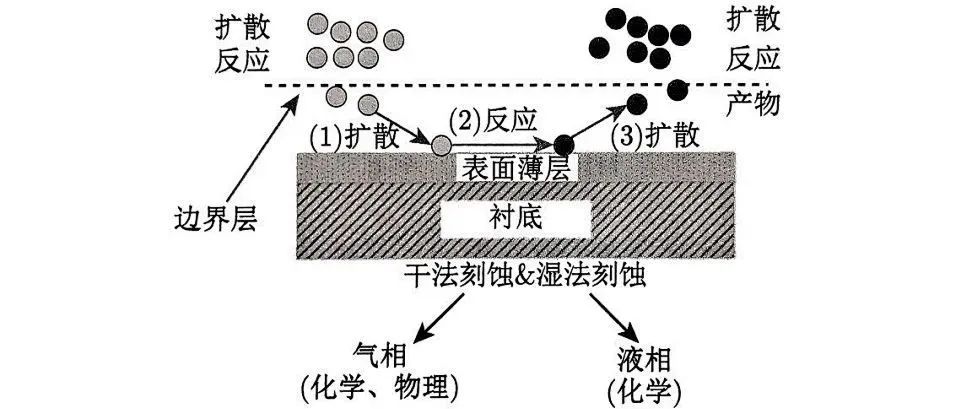

干法刻蝕技術(shù)作為半導(dǎo)體制造的核心工藝模塊,通過等離子體與材料表面的相互作用實(shí)現(xiàn)精準(zhǔn)刻蝕,其技術(shù)特性與....

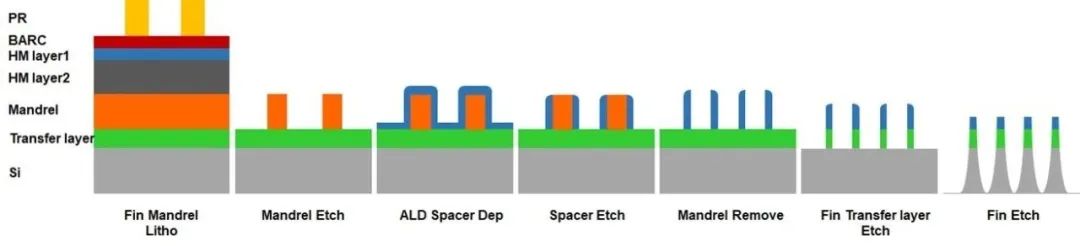

自對(duì)準(zhǔn)雙重圖案化技術(shù)的優(yōu)勢(shì)與步驟

在芯片制造中,光刻技術(shù)在硅片上刻出納米級(jí)的電路圖案。然而,當(dāng)制程進(jìn)入7納米以下,傳統(tǒng)光刻的分辨率已逼....

一文詳解濕法刻蝕工藝

濕法刻蝕作為半導(dǎo)體制造領(lǐng)域的元老級(jí)技術(shù),其發(fā)展歷程與集成電路的微型化進(jìn)程緊密交織。盡管在先進(jìn)制程中因....

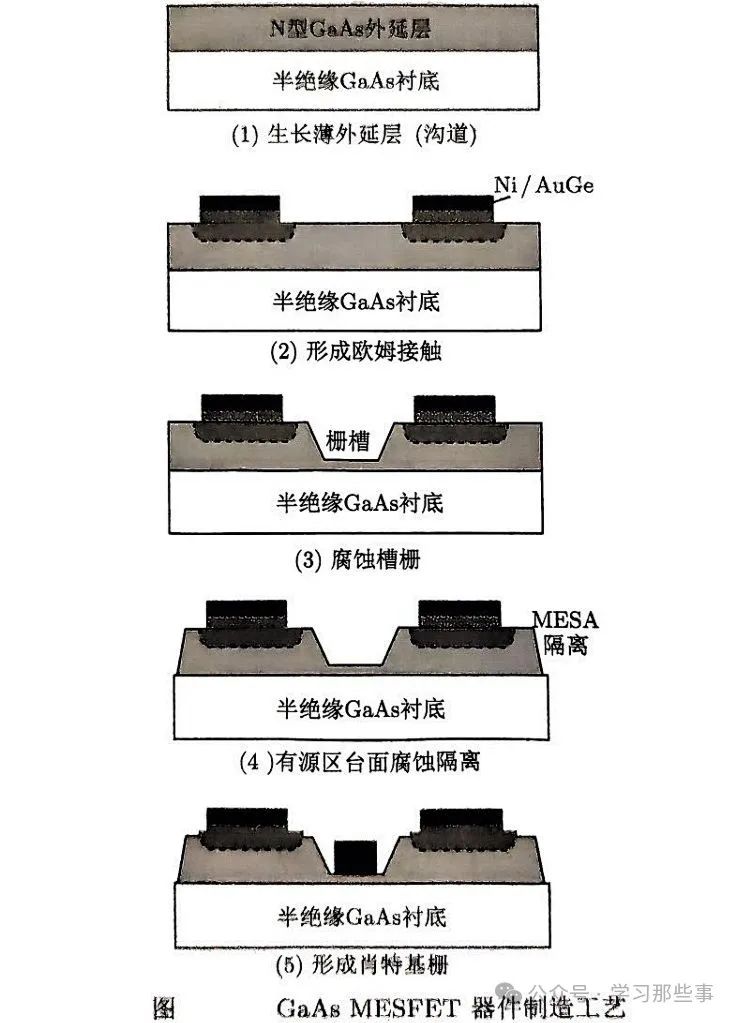

化合物半導(dǎo)體器件的定義和制造工藝

化合物半導(dǎo)體器件以Ⅲ-Ⅴ族、Ⅱ-Ⅵ族元素通過共價(jià)鍵形成的材料為基礎(chǔ),展現(xiàn)出獨(dú)特的電學(xué)與光學(xué)特性。以砷....

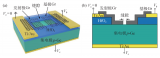

薄膜晶體管技術(shù)架構(gòu)與主流工藝路線

導(dǎo)語薄膜晶體管(TFT)作為平板顯示技術(shù)的核心驅(qū)動(dòng)元件,通過材料創(chuàng)新與工藝優(yōu)化,實(shí)現(xiàn)了從傳統(tǒng)非晶硅向....

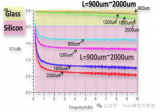

玻璃通孔技術(shù)的五個(gè)獨(dú)特優(yōu)勢(shì)

TGV(Through Glass Via)工藝之所以選擇在玻璃上打孔,主要是因?yàn)椴Aг谝韵挛鍌€(gè)方面....

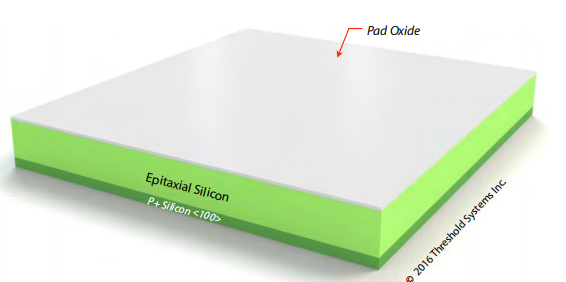

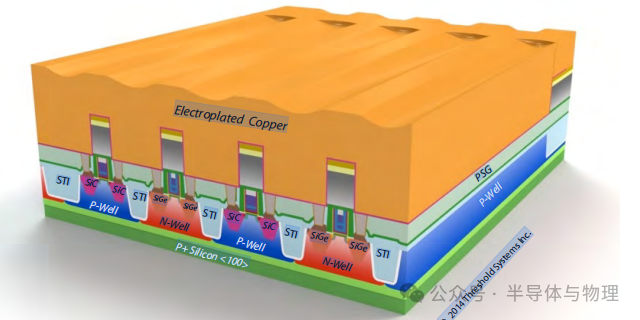

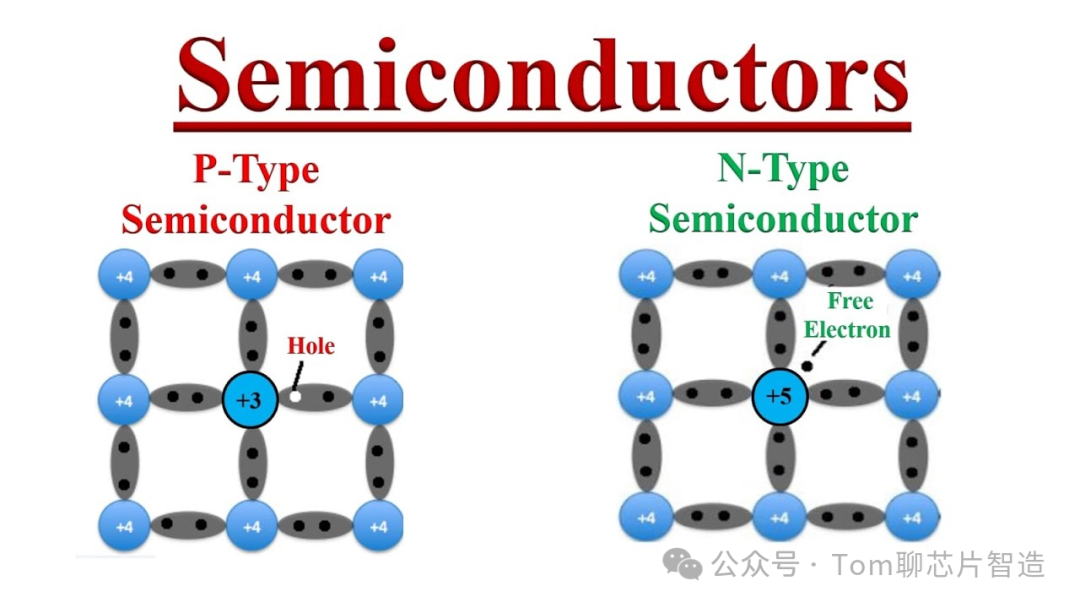

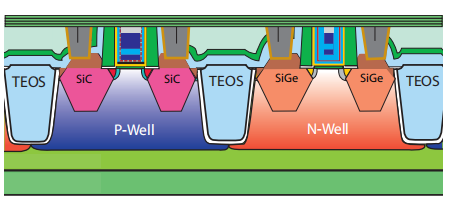

CMOS工藝流程簡(jiǎn)介

互補(bǔ)金屬氧化物半導(dǎo)體(CMOS)技術(shù)是現(xiàn)代集成電路設(shè)計(jì)的核心,它利用了N型和P型MOSFET(金屬氧....

低功耗熱發(fā)射極晶體管的工作原理與制備方法

集成電路是現(xiàn)代信息技術(shù)的基石,而晶體管則是集成電路的基本單元。沿著摩爾定律發(fā)展,現(xiàn)代集成電路的集成度....

一文詳解快速熱處理技術(shù)

在納米尺度集成電路制造領(lǐng)域,快速熱處理(RTP)技術(shù)已成為實(shí)現(xiàn)器件性能突破與工藝優(yōu)化的核心工具。相較....

定向自組裝光刻技術(shù)的基本原理和實(shí)現(xiàn)方法

定向自組裝光刻技術(shù)通過材料科學(xué)與自組裝工藝的深度融合,正在重構(gòu)納米制造的工藝組成。主要內(nèi)容包含圖形結(jié)....

FinFET與GAA結(jié)構(gòu)的差異及其影響

本文介紹了當(dāng)半導(dǎo)體技術(shù)從FinFET轉(zhuǎn)向GAA(Gate-All-Around)時(shí)工藝面臨的影響。

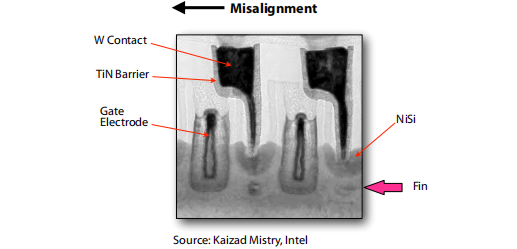

芯片制造中自對(duì)準(zhǔn)接觸技術(shù)介紹

但當(dāng)芯片做到22納米時(shí),工程師遇到了大麻煩——用光刻機(jī)畫接觸孔時(shí),稍有一點(diǎn)偏差就會(huì)導(dǎo)致芯片報(bào)廢。 自....

芯片前端設(shè)計(jì)與后端設(shè)計(jì)的區(qū)別

前端設(shè)計(jì)(Front-end Design):聚焦于電路的邏輯功能實(shí)現(xiàn)。本質(zhì)上是在“紙上”設(shè)計(jì)電路,....

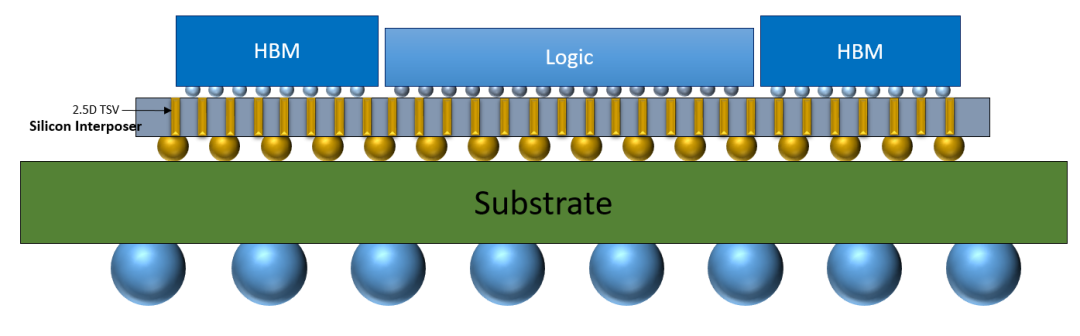

詳細(xì)解讀三星的先進(jìn)封裝技術(shù)

集成電路產(chǎn)業(yè)通常被分為芯片設(shè)計(jì)、芯片制造、封裝測(cè)試三大領(lǐng)域。其中,芯片制造是集成電路產(chǎn)業(yè)門檻最高的行....

芯片前端設(shè)計(jì)中常用的軟件和工具

前端設(shè)計(jì)是數(shù)字芯片開發(fā)的初步階段,其核心目標(biāo)是從功能規(guī)格出發(fā),最終獲得門級(jí)網(wǎng)表(Netlist)。這....

為什么芯片需要低介電常數(shù)材料

在現(xiàn)代芯片中,數(shù)十億晶體管通過金屬互連線連接成復(fù)雜電路。隨著制程進(jìn)入納米級(jí),一個(gè)看似“隱形”的問題逐....

電子顯微鏡中的磁透鏡設(shè)計(jì)

十九世紀(jì)末,科學(xué)家首次觀察到軸對(duì)稱磁場(chǎng)對(duì)陰極射線示波器中電子束產(chǎn)生的聚焦作用,這種效應(yīng)與光學(xué)透鏡對(duì)可....

化學(xué)機(jī)械拋光液的基本組成

化學(xué)機(jī)械拋光液是化學(xué)機(jī)械拋光(CMP)工藝中關(guān)鍵的功能性耗材,其本質(zhì)是一個(gè)多組分的液體復(fù)合體系,在拋....