隨著半導體器件尺寸的不斷縮小和性能要求的日益提高���,應變工程半導體異質(zhì)結(jié)構(gòu)在現(xiàn)代電子器件中發(fā)揮著關(guān)鍵作....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-27 09:12

?1276次閱讀

本文簡單介紹一下半導體鍍膜的相關(guān)知識,基礎(chǔ)的薄膜制備方法包含熱蒸發(fā)和濺射法兩類�����。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-26 14:03

?943次閱讀

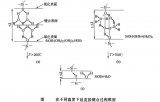

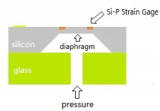

相比傳統(tǒng)體加工技術(shù),表面微機械加工通過“犧牲層腐蝕”工藝�,可構(gòu)建更復雜的三維微結(jié)構(gòu),顯著擴展設計空間....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-26 14:01

?531次閱讀

在半導體制造領(lǐng)域����,晶體管結(jié)構(gòu)的選擇如同建筑中的地基設計,直接決定了芯片的性能上限與能效邊界���。當制程節(jié)....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-25 16:49

?1363次閱讀

“基帶”這個詞�����,最早來源于通信理論�,意思是未經(jīng)調(diào)制的原始信號�。比如你打電話時說話的聲音、視頻通話中的....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-25 15:37

?1194次閱讀

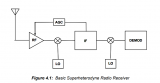

射頻電路是處理高頻信號的電路�,在無線通信系統(tǒng)中發(fā)揮著至關(guān)重要的作用。它們負責接收���、發(fā)射和處理射頻信號....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-20 16:13

?793次閱讀

本文是A. N. BROERS關(guān)于掃描電鏡在微納加工中應用的研究回顧��,重點記錄了他從1960年代開始....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-20 16:11

?711次閱讀

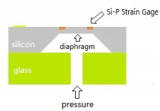

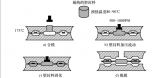

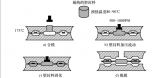

硅片鍵合作為微機械加工領(lǐng)域的核心技術(shù)���,其工藝分類與應用場景的精準解析對行業(yè)實踐具有重要指導意義���。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-20 16:09

?660次閱讀

傳統(tǒng)的透射電鏡(TEM)技術(shù)往往只能提供材料在靜態(tài)條件下的結(jié)構(gòu)信息����,無法滿足科研人員對材料在實際應用....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-19 16:28

?630次閱讀

在 MEMS(微機電系統(tǒng))制造領(lǐng)域,光刻工藝是決定版圖中的圖案能否精確 “印刷” 到硅片上的核心環(huán)節(jié)....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-18 11:30

?965次閱讀

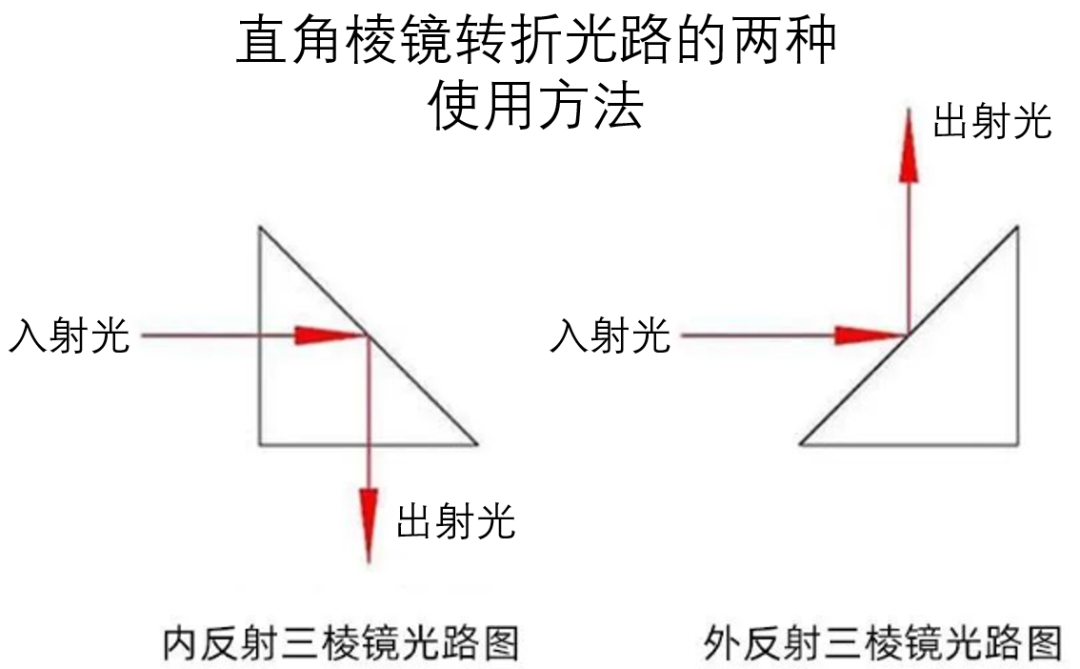

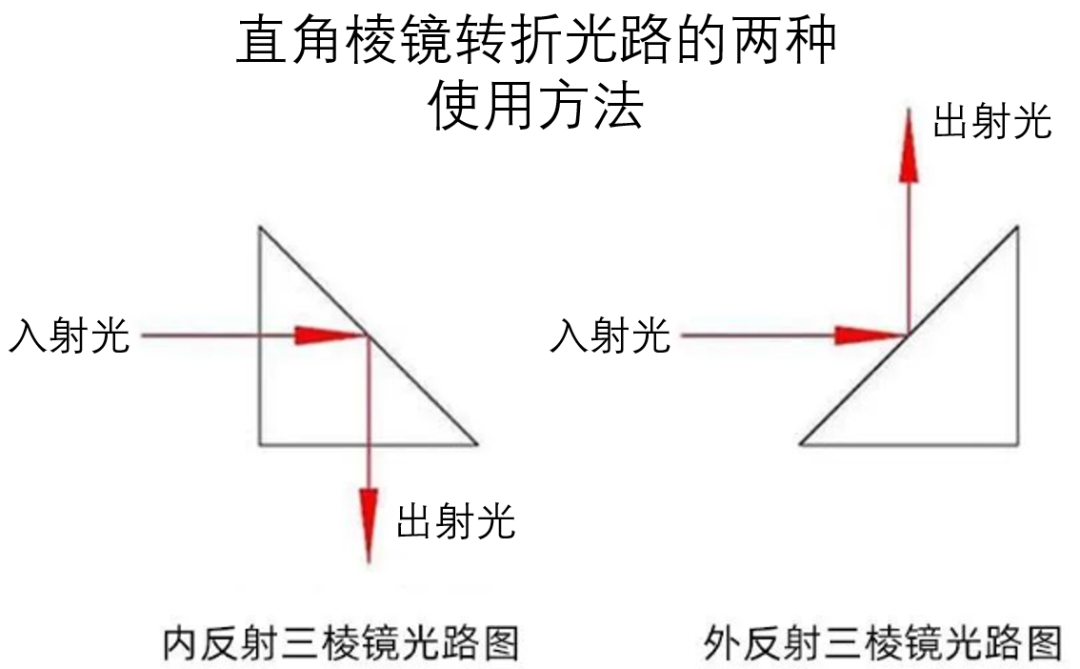

光學直角棱鏡是一種常見的光學元件���,它能夠?qū)⒐饩€的傳播方向精確地偏轉(zhuǎn)90度�����。這種功能看似簡單��,卻在許多....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-17 16:20

?880次閱讀

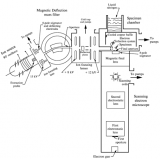

聚焦離子束(FIB)在材料科學和微納加工領(lǐng)域內(nèi)的重要性日益顯現(xiàn)���,離子束的傳輸過程由多個關(guān)鍵組件構(gòu)成,....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-17 15:47

?555次閱讀

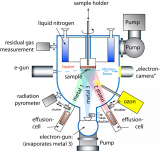

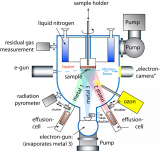

高質(zhì)量的材料制備是一切器件研究的核心與基礎(chǔ),本篇文章主要講述MBE的原理及制備過程?

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-17 15:05

?773次閱讀

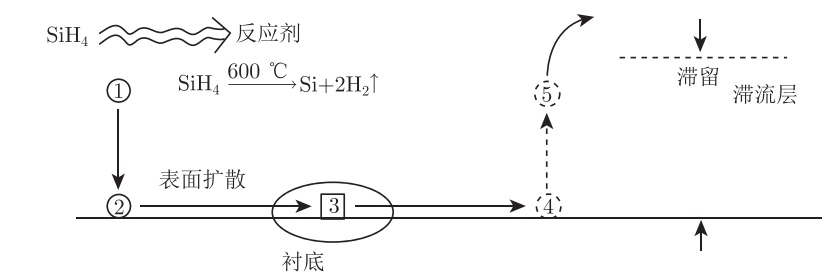

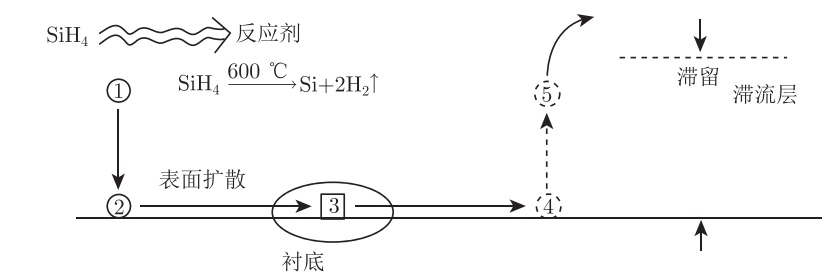

隨著半導體器件特征尺寸不斷微縮�,對高質(zhì)量薄膜材料的需求愈發(fā)迫切。外延技術(shù)作為一種在半導體工藝制造中常....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-16 11:44

?1861次閱讀

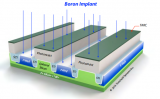

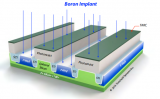

在芯片的硅基世界中�����,硼離子注入(Boron Implant) 如同納米級的外科手術(shù)——通過精準控制高....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-13 11:43

?516次閱讀

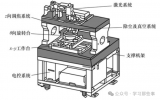

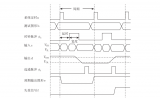

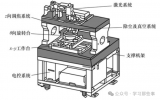

激光劃片機是利用高能激光束對晶圓等材料進行切割或開槽的精密加工設備,廣泛應用于半導體��、微電子��、光學器....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-13 11:41

?1450次閱讀

晶圓經(jīng)切割后�,表面常附著大量由聚合物、光致抗蝕劑及蝕刻雜質(zhì)等組成的顆粒物��,這些物質(zhì)會對后續(xù)工序中芯片....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-13 09:57

?619次閱讀

在5納米以下的芯片制程中��,晶體管柵極介質(zhì)層的厚度已縮至1納米以下(約5個原子層)��。此時�,傳統(tǒng)二氧化硅....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-12 14:11

?1756次閱讀

所謂塑封,是指將構(gòu)成電子元器件或集成電路的各部件按規(guī)范要求進行合理布置��、組裝與連接�,并通過隔離技術(shù)使....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-12 14:09

?2093次閱讀

在集成電路制造工藝中,氧化工藝也是很關(guān)鍵的一環(huán)���。通過在硅晶圓表面形成二氧化硅(SiO?)薄膜�����,不僅可....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-12 10:23

?1533次閱讀

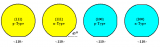

硅晶圓揀選測試作為半導體制造流程中的關(guān)鍵質(zhì)量控制環(huán)節(jié)���,旨在通過系統(tǒng)性電氣檢測篩選出功能異常的芯片����。該....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-11 09:49

?972次閱讀

引線框架(Lead Frame)是一種金屬結(jié)構(gòu)���,主要用于半導體芯片的封裝中,作用就像橋梁——它連接芯....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-09 14:55

?1163次閱讀

在功率半導體制程里�����,電鍍扮演著舉足輕重的角色�����,從芯片前端制程到后端封裝����,均離不開這一關(guān)鍵工序。目前��,....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-09 14:52

?1603次閱讀

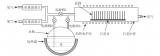

ISSG(In-Situ Steam Generation��,原位水蒸汽生成)是半導體制造中的一種高溫....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-07 09:23

?3108次閱讀

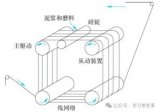

通過單晶生長工藝獲得的單晶硅錠��,因硅材質(zhì)硬脆特性,無法直接用于半導體芯片制造���,需經(jīng)過機械加工�����、化學處....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-06 14:10

?476次閱讀

晶面和晶向是晶體學中兩個核心的概念���,它們與硅基集成電路工藝中的晶體結(jié)構(gòu)有密切的關(guān)系。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-05 16:58

?2115次閱讀

晶圓級扇出封裝(FO-WLP)通過環(huán)氧樹脂模塑料(EMC)擴展芯片有效面積�����,突破了扇入型封裝的I/O....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-05 16:25

?1642次閱讀

本文介紹了在射頻前端模塊(RF-FEM)中使用的集成無源元件(IPD)技術(shù)�����。

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-03 18:26

?896次閱讀

打線鍵合就是將芯片上的電信號從芯片內(nèi)部“引出來”的關(guān)鍵步驟����。我們要用極細的金屬線(多為金線、鋁線或銅....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-03 18:25

?1265次閱讀

自半導體晶體管問世以來�,集成電路技術(shù)便在摩爾定律的指引下迅猛發(fā)展。摩爾定律預言����,單位面積上的晶體管數(shù)....

![的頭像]() 中科院半導體所 發(fā)表于

中科院半導體所 發(fā)表于 06-03 18:24

?986次閱讀