IMD1工藝是指在第一層金屬之間的介質(zhì)隔離材料��。IMD1的材料是 ULK (Ultra Low K)....

金屬層1工藝是指形成第一層金屬互連線��,第一層金屬互連線的目的是實(shí)現(xiàn)把不同區(qū)域的接觸孔連起來��,以及把不....

ILD 工藝是指在器件與第一層金屬之間形成的介質(zhì)材料��,形成電性隔離�����。ILD介質(zhì)層可以有效地隔離金屬互....

Salicide 工藝是指在沒有氧化物覆蓋的襯底硅和多晶硅上形成金屬硅化物�����,從而得到低阻的有源區(qū)和多....

與亞微米工藝類似�,源漏離子注入工藝是指形成器件的源漏有源區(qū)重?fù)诫s的工藝,降低器件有源區(qū)的串聯(lián)電阻���,提....

與亞微米工藝類似�,側(cè)墻工藝是指形成環(huán)繞多晶硅的氧化介質(zhì)層�,從而保護(hù)LDD 結(jié)構(gòu),防止重?fù)诫s的源漏離子....

與亞微米工藝類似���,多晶硅柵工藝是指形成 MOS器件的多晶硅柵極����,柵極的作用是控制器件的關(guān)閉或者導(dǎo)通�。....

與亞微米工藝類似,柵氧化層工藝是通過熱氧化形成高質(zhì)量的柵氧化層����,它的熱穩(wěn)定性和界面態(tài)都非常好。

與亞微米工藝類似���,雙阱工藝是指形成NW和PW的工藝�����,NMOS 是制造在PW里的�����,PMOS是制造在NW....

STI 隔離工藝是指利用氧化硅填充溝槽�,在器件有源區(qū)之間嵌入很厚的氧化物,從而形成器件之間的隔離����。利....

有源區(qū)工藝是指通過刻蝕去掉非有源區(qū)的區(qū)域的硅襯底,而保留器件的有源區(qū)��。

集成電路的可靠性與內(nèi)部半導(dǎo)體器件表面的性質(zhì)有密切的關(guān)系��,目前大部分的集成電路采用塑料封裝而非陶瓷封裝....

頂層金屬工藝是指形成最后一層金屬互連線�����,頂層金屬互連線的目的是實(shí)現(xiàn)把第二層金屬連接起來�。頂層金屬需要....

IMD2 工藝與 IMD1工藝類似。IMD2 工藝是指在第二層金屬與第三層金屬之間形成的介質(zhì)材料�����,形....

金屬層2(M2)工藝與金屬層1工藝類似�。金屬層2工藝是指形成第二層金屬互連線,金屬互連線的目的是實(shí)現(xiàn)....

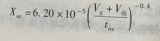

隨著器件的特征尺寸減少到90mm 以下����,柵氧化層厚度也不斷減小,載流子的物理特性不再遵從經(jīng)典理論���,其....

隨著集成電路工藝技術(shù)的不斷發(fā)展�,為了提高集成電路的集成度�,同時提升器件的工作速度和降低它的功耗,集成....

當(dāng)柵與襯底之間存在壓差時�,它們之間存在電場,靜電邊界條件使多晶硅靠近氧化層界面附近的能帶發(fā)生彎曲���,并....

SMT僅僅是用來提高NMOS 的速度�,當(dāng)工藝技術(shù)發(fā)展到45nm 以下時�,半導(dǎo)體業(yè)界迫切需要另一種表面....

應(yīng)力記憶技術(shù)(Stress Memorization Technique, SMT),是一種利用覆蓋....

與通過源漏嵌入 SiC 應(yīng)變材料來提高NMOS 的速度類似���,通過源漏嵌入 SiGe 應(yīng)變材料可以提高....

源漏區(qū)嵌入SiC 應(yīng)變技術(shù)被廣泛用于提高90nm 及以下工藝制程 NMOS 的速度�,它是通過外延生長....

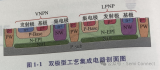

按照基本工藝制程技術(shù)的類型��,BiCMOS 工藝制程技術(shù)又可以分為以 CMOS 工藝制程技術(shù)為基礎(chǔ)的 ....

BCD 工藝制程技術(shù)只適合某些對功率器件尤其是BJT 或大電流 DMOS 器件要求比較高的IC產(chǎn)品�。....

1986年,意法半導(dǎo)體(ST)公司率先研制成功BCD工藝制程技術(shù)���。BCD工藝制程技術(shù)就是把BJT��,C....

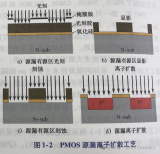

PMOS(Positive channel Metal Oxide Semiconductor���,P ....

本章主要介紹了集成電路是如何從雙極型工藝技術(shù)一步一步發(fā)展到CMOS 工藝技術(shù)以及為了適應(yīng)不斷變化的應(yīng)....

觀察矽晶圓的外緣�����,可以發(fā)現(xiàn)有如圖4-6-1所示的邊緣磨邊加工�。此種針對外緣進(jìn)行磨邊的加工����,一般稱為“....

完成打線的半導(dǎo)體晶片,為了防止外界物理性接觸或污染的侵入�����,需要以包裝或是封裝材料密封���。

在半導(dǎo)體記憶體中�����,例如一個1G的DRAM�,代表一個半導(dǎo)體晶片上擁有10億個能夠記憶1 bit的資訊單....